相变存储单元仿真电路设计

本文提出一种基于分立元件的相变存储器(PCM)仿真电路,可在LTSpice中建模并用CMOS 0.35微米技术实现。该电路复现了PCM的温度响应、阈值开关、电阻编程及标准电流-电压特性,仿真与实验结果与实际GST器件数据高度吻合,适用于教学与应用开发。

相变存储单元仿真电路设计

目录列表可在 ScienceDirect 微电子学杂志期刊主页: www.elsevier.com/locate/mejo

关键词 :相变存储器 奥冯尼记忆 阈值开关 硫属化物 非易失性存储器 仿真器 分立元件

摘要

本文提出了一种全新的相变存储器(PCM)单元仿真电路设计,该电路完全由现成的分立电子元件构成。所设计的仿真电路能够重现相变存储单元在单元温度、阈值电压以及对给定输入的编程电阻水平方面的行为。该电路在 LTSpice 仿真环境中进行设计和测试,并采用 CMOS 0.35 微米技术及其他现成分立元件实现。所设计的仿真电路成功生成了相变存储单元的操作特性。该仿真电路评估了编程时间的影响,产生了相变存储元件的标准电流‐电压特性,并在整个运行期间保持了存储的数据。此外,所设计仿真电路的仿真与实验结果与实际基于 Ge2Sb2Te5 (GST) 的相变存储元件所获得的实验数据非常吻合。

1. 引言

当前计算机存储层次结构在易失性(SRAM、DRAM)和非易失性(闪存)存储器之间存在性能差距;体现在运行速度、密度和功耗方面。这促使需要一种新型存储器,能够通过兼具易失性存储器(VM)的运行速度和非易失性存储器(NVM)的耐久性、密度及低功耗来弥合这一差距[1]。近年来,新兴的阻变存储技术被广泛研究,可用于弥合传统存储层次结构中的差距,在计算中[2], 提升缓存存储性能 [3,4], 以及替代 flash 存储器,在技术文献中受到广泛关注 [5–10]。这些新兴的非易失性技术具有低功耗、高速运行、长数据保持和高可扩展性等优点,从而实现高密度。

阻变存储器的工作原理基于以下事实:通过施加外部电势可以控制存储单元的等效电阻,从而引起单元电阻的变化。这种电阻切换可以通过电方式(如忆阻器)、磁方式(如磁隧道结(MTJ)和铁电随机存取存储器(FeRAM))或热方式(如相变存储器(PCM))[11,12] 来实现。因此,存储单元可通过处于两种电阻状态之一来存储二进制数据;其中相对较高的高阻态对应“0”,相对较低的电阻状态代表“1”。

本研究聚焦于相变存储器,因其具备高性能特性,使其在除传统应用外的其他领域中成为一种极具潜力且理想的选择存储器。例如处理器[13], 空间应用[14], 以及作为构建类脑系统的电子突触元件[15]。由于相变存储器具有如此广泛的应用前景,因此需要一个全面且描述性强的相变存储器元件模型。研究人员已开发出许多仿真模型[16–21];但为了物理实现并测试相变存储器的行为,并充分利用其在各种应用中的潜力,需要一个仿真器。该仿真器由能够模拟相变存储单元行为的电路构成。通过该电路,可以在无需承担制造纳米级器件的成本和技术困难的情况下,设计和开发相变存储器的应用。仿真器也被视为一种有效的学习工具,通过简单地组装分立元件,即可测试和研究相变存储器的电学特性。

在技术文献中,已有多种针对其他非易失性存储器技术的仿真器模型,例如忆阻器[22–25], 和 NAND flash[26]。文献[26] 中提出的仿真器模型为评估基于现场可编程门阵列的非易失性存储器中的循环耐久性影响提供了平台。然而,其重点在于 NAND flash 技术,并仅提出该工作可扩展至支持相变存储器。因此,据我们撰写本文时所知,技术文献中唯一提出的相变存储器仿真电路是[27]。尽管已有多个仿真模型被提出[16–21],其中[16,17,19,21] 提出的基于 Verilog‐A 的模型用于相变存储器。然而,[16,19,21] 中的模型并未提出任何电路设计,因此不一定能保证仿真结果的有效性。此外,[19,20] 中的模型无法生成相变存储单元的电流‐电压特性。与其他仿真模型相比,本文提出的模型提出了一种[18] 考虑了电压负阻现象并成功生成了电流‐电压特性的方法。因此,该方法被用作本文提出的仿真电路设计的基准。此外,[27] 中提出的仿真电路缺乏识别电阻对阈值电压依赖性的能力,且未充分表征编程时间的影响。本文提出的仿真电路设计解决了这些问题。

本文提出了一种完全由现成分立元件构成的仿真电路设计,该电路易于构建和测试。所提出的仿真器可作为实际相变存储单元的电路替代品,用于探索相变存储器(PCM)的潜在应用,并作为理解 PCM 操作基础的教学工具。该仿真器首先借助 SPICE 工具(LTSpice IV)进行设计。在基于 SPICE 的模型经过测试和验证后,采用 CMOS 0.35 微米技术实现建议的仿真器电路,并进行测试以验证其行为特性。

与忆阻器仿真器类似[22–24];设计并构建的相变存储器仿真电路具有实际相变存储器元件的操作特性。需要注意的是,该仿真电路能够生成非易失性存储器件的操作特性,即电流‐电压响应,并以电阻形式在操作期间保持存储的数据。然而,仿真电路的能耗与所使用的硬件组件相关,无法与实际的非易失性存储器件直接关联。尽管如此,设计的仿真电路重现了其他操作特性,包括温度分布、电阻行为和标准的电流‐电压特性。此外,从设计并构建的电路获得的结果与实验数据进行了比较,发现与实际相变存储器元件的实验数据非常吻合。

本文其余部分的布局如下: 第2节 解释了相变存储器元件的操作特性。设计的仿真电路在 第3节 中进行了详细描述。实验和仿真结果在 第4节 中给出并讨论。最后,论文在 第5节 中得出结论。

2. 相变存储器的操作概念

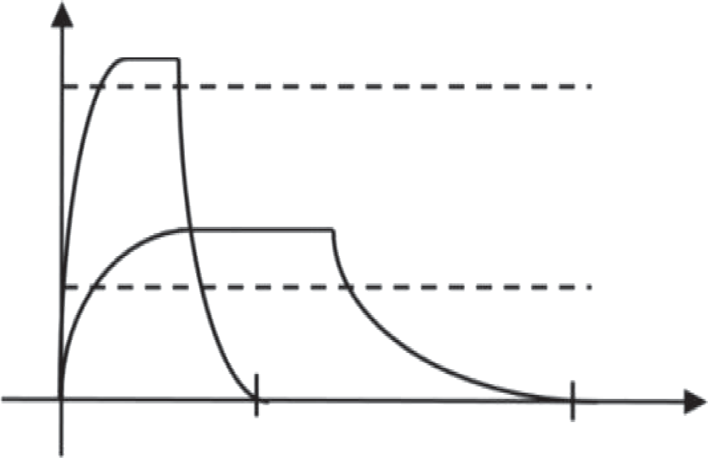

相变材料的可控电阻被用来存储数据,通过为每个电阻级别分配一个二进制等效值,即高电阻(RRESET)表示“0” ,低电阻(RSET)表示“1”。目标电阻通过利用焦耳热效应实现。要将相变存储单元编程至非晶高阻相(RESET),需施加一个陡峭脉冲,使相变材料熔化后迅速冷却,如图1所示。而要将相变存储单元编程至低阻态晶相(SET),则施加一个较低幅度的脉冲。该脉冲使温度升高至超过 GST 的结晶温度(Tcryt)但远低于熔化温度(Tmelt),并保持足够长的时间以使相变材料结晶,如图1所示。

基因由于输入信号(Vin)产生的额定焦耳热(W j)can be 通过(1)进行评估。相变存储单元(Tcell)上的温度作为输入的函数,通过传热方程(2)进行评估,其中 r1 和 r2 分别为有源层厚度和 GST 层的厚度。k 为热导率,t 为时间,C 为热容[19]。

$$ W= V × I j in cell $$ (1)

$$ \left( \right) T= 0. 7W(r − r) 2πkr r 1−exp − 3kr (r − r)r c t +25 cell j 2 1 2 1 2 2 1 1 2 $$ (2)

通过考虑图 2[28] 所示的标准相变存储单元的电流‐电压特性,可以理解编程和读取过程。当在初始处于高电阻非晶态(RRESET)的单元上施加高于阈值的电压时,会发现非晶相表现出开关行为,并在此时发生负阻现象。随后,非晶区的电阻转变为较低的电阻状态(RON)。如果该电压维持足够长的时间,则会发生结晶过程,此过程被称为置位过程。

另一方面,如果存储单元处于晶态(RSET),并施加一个足够使温度升高至 GST 熔点以上的陡峭电压脉冲,如图2所示,则会发生向非晶态的相变。该过程称为复位过程。需要注意的是,非晶态结构的阈值电压 Vthmax 大于晶态结构的阈值电压 Vthmin。此外,为了读取相变存储单元,需施加低于阈值电压的电压,以避免意外编程。然后通过测量流过存储单元的电流来评估单元的电阻,因为非晶态与晶相之间存在大的电阻比。

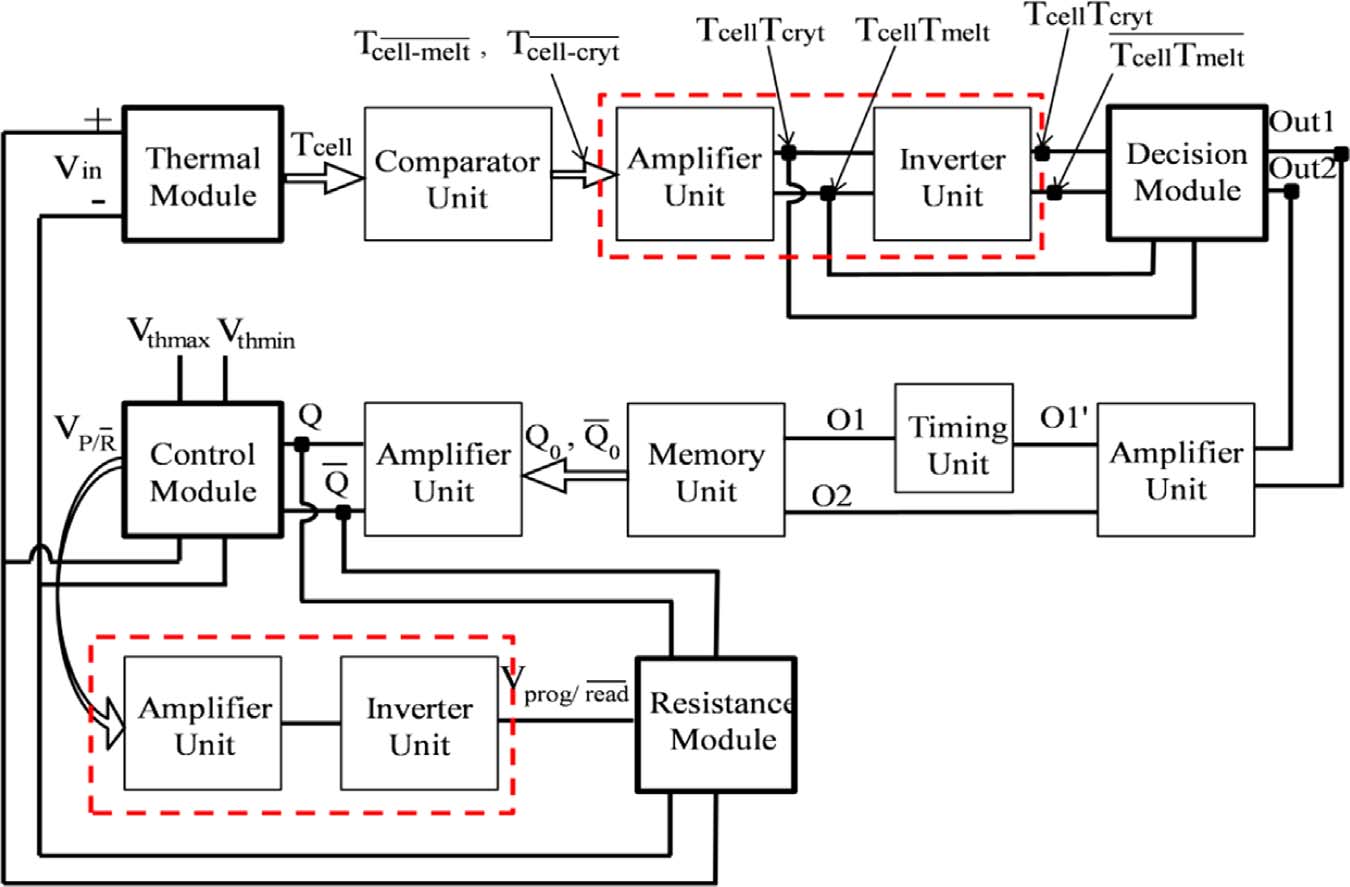

3. 相变存储单元模拟器电路

设计的仿真电路由互连的主要模块构成,即热模块、决策模块、控制模块和电阻模块,如图3所示。每个模块接收来自其他模块的一个或多个输入,并相应地生成输出。该输出随后被放大和/或反相后传递给下一个模块。热模块根据输入信号估算相变存储单元两端的等效温度。而决策模块与控制模块则评估施加脉冲的热范围,并据此判断存储单元正处于编程还是读取状态。如果处于编程状态,则进一步确定其将被置为两种可能状态中的哪一种,即置位(SET)或复位(RESET)。最后,电阻模块估算存储单元的等效电阻,即存储的比特值。当这些互连单元正常工作时,便能够重现单个相变存储器单元的操作特性。下文将对图 3 中所示的 proposed 仿真电路设计进行详细描述。此外,还包括主要模块与中间单元之间互连的动态特性,以及所使用的离散

3.1. 热模块

热模块电路设计用于根据施加的脉冲估算单元温度。为了构建基于分立元件的温度计算电路,在电压分压器结构 R1 和 R2 中引入了一个硅二极管 D1,如图4所示。该二极管产生一个指数响应,该响应类似于实际 PCM 单元中的温度变化,如(2)所述。电阻 R2 两端在节点 Tcell 的电压等效于单元上的温度。需要注意的是,在设计的仿真电路中,温度以等效电压表示。此外,时间单位为秒,而非实际 PCM 单元工作的纳米级时间尺度。但通过适当的缩放以及电阻值的选择,可以仿真实际 PCM 单元的行为。所估算的单元温度等效值随后被决策模块使用,在与基于 GST 的 PCM 单元的编程温度等效值(即结晶温度(Tcryt)和熔化温度(Tmelt))比较后进行判断。

3.2. 比较器单元

为了确定施加在 PCM 单元上的操作,必须将温度模块输出的 Tcell 与编程温度进行比较。如果施加的脉冲使单元两端的温度 Tcell 保持在 Tcr y t 以下,则正在对相变存储单元执行读取操作。如果 Tcell 高于 Tcr y t 但低于熔化温度 Tmelt,则相变存储器正在被编程至晶相。然而,如果 Tcell 高于 Tmelt,则相变存储器正在被编程至非晶相。因此,为了执行必要的比较,使用由运算放大器构成的比较器单元。该比较器单元利用 UA741 运算放大器将 Tcell 与 Tmelt 和 Tcryt 进行比较,以选择单元的温度,如图5所示。

3.3. 放大器和反相器单元

比较器单元生成 Tcell cryt−和 Tcell melt−信号;指示 Tcell 与编程温度 Tcryt 和 Tmelt 的比较结果。这些信号将由决策模块用于识别所提示的操作。此外,决策模块还需要这些信号的反相信号,这将在 第3.4节 中描述。然而,比较器输出的电流不足以驱动反相器和决策电路中的所有晶体管(共8个晶体管)。因此,需对信号进行放大后再反相,以在适当电流下提供所需值,确保设计的电路正确操作。

放大单元采用如图6(a)所示的 UA741 放大器构成;用于增强比较器输出。使用了两个放大器单元,输入(In)分别连接至 Tcell−cryt 和 T cell−melt;以便在输出(Out)端产生放大的 T Tcell cryt 和 T Tcell melt。放大后的 T Tcell cryt 和 T Tcell melt 随后通过两个如图6(b)所示的反相器单元进行反相。该反相器单元采用标准通用 NPN 晶体管构成。T T cell cryt 和 T Tcell melt 连接至反相器单元的输入端(In),以在输出端(Out)生成 T Tcell cryt 和 T Tcell melt。比较器单元的放大并反相的输出信号随后被决策模块使用,以识别输入信号正在尝试执行何种操作。

放大单元,和 (b) 逆变器单元。)

3.4. 决策模块

设计决策电路时,需列出决策电路的预期真值表,即表1。根据单元温度,该电路的预期输出用于指示单元处于以下哪种状态:(a) 被编程为非晶态,或 (b) 晶态,或 (c) 正在读取。由于输出需要区分三种不同状态,因此该电路至少需要两个输出,即 输出1 和 输出2。

基于 表1,设计了一个利用图7(a)所示卡诺图的电路,得到(输出 1= T Tcell melt 与门 T Tcell cryt)和(输出 2=T Tcell melt)。用于生成输出 1 的与门采用逻辑开关和标准通用 NPN 晶体管设计,如图7(b)所示。然后,以类似于温度比较器放大器的方式;输出1和输出2均分别被放大为 O1’ 和 O2。这是为了使信号能够被足以驱动后续电路。

| 温度 | 操作 | TcellTmelt | TcellT cryt | Out1 | Out2 |

|---|---|---|---|---|---|

| Tcell<Tcryt | Read | 1 | 1 | 0 | 0 |

| Tcryt< Tcell< Tmelt | SET | 1 | 0 | 1 | 0 |

| Tmelt< Tcell | 复位 | 0 | 0 | 0 | 1 |

表1 决策模块的真值表。

3.5. 定时单元

O1’ 在一个包含充电电容的定时单元中进行处理,如 图8 所示。在此阶段使用电容的目的是将脉冲持续时间对相变存储单元编程的影响纳入考虑,即仿真电路中电容充电所需的时间可视为相变存储单元结晶所需时间的等效值。该机制仅应用于 O1’,而不应用于 O2,因为 O1’ 是指示结晶过程的信号。

3.6. 存储单元

为了保留先前编程状态,采用了一个 RS flipflop 锁存器(图9(a)),作为单比特存储器使用。该基于或非门的锁存器由标准通用 NPN 晶体管构成,如 图9(b) 所示。增强的决策模块输出(即 O1 和 O2)被用作输入,锁存器中存储的位 “Q0” 表示先前编程的位,如 图9(a) 所示。

此外,锁存器输出即 Q0 和 Q0 被进一步放大,以产生足够的信号来正确驱动下一级电路。放大方式与前级类似;使用两个放大单元(图 6(a))将 Q0 和 Q0 分别提升为 Q 和 Q。只要仿真电路供电,先前编程状态 Q 就会保持不变。然后 Q 和 Q 用作控制模块电路中基于 NPN 晶体管的电子开关的控制输入。

3.7. 控制模块

控制模块根据输入脉冲判断单元是处于编程还是读取状态。这是通过将施加电压与编程发生的阈值电压进行比较来实现的。但由于相变存储单元在实验上对每个电阻阶段表现出不同的阈值电压,因此存在两个阈值电压。Vthmax 和 Vthmin 分别是高阻态和低阻态的阈值电压分别表示。单元的先前编程状态,即 Q 和 Q 决定了当前的阈值电压,如图 10 所示。然后,控制电路的比较器输出(VP/R)如图10 所示,通过比较输入电压和阈值电压来指示单元是处于编程还是读取状态。

此外,控制模块的输出被进一步放大为 $(V) {prog/read}$ 并反相为 $(V) {prog/read}$,以供电阻模块使用。这一过程与之前使用图6中的放大器和反相器电路的方式类似。

3.8. 电阻模块

电阻模块表示相变存储单元的等效电阻。当施加读取脉冲时,该单元处于先前编程状态;当单元经受编程脉冲时,其表现为动态电阻 RON 。输入脉冲 Vin 如图11所示施加到电阻模块上,流经 Rtest 的电流可被测量,并与输入电压一起用于估算存储单元的等效电阻。根据控制和决策模块的输出,确定该等效电阻。这些输出用于控制基于 NMOS 的电子开关,如图11所示。因此,决定电流在三条可能路径中的流动路径,即通过 R ON、RSET 或 RRESET,并相应地确定相变存储单元的等效电阻。

需要注意的是,所选材料在非晶态和晶态下的电导率(ρ),以及相变存储单元的尺寸,即厚度(l)和面积(A),决定了 RON、RSET 和 R RESET 的值,如公式(3)所示。在本研究中,选择了对应特定尺寸(即 90 纳米厚度和 4000 nm² 底接触面积[28])的 RON、RSET 和 RRESET 值,以便将仿真器得到的结果与文献[28] 中提供的相变存储单元的实验数据进行比较。

$$ R = \frac{\rho l}{A} $$ (3)

4. 仿真与实验结果

仿真结果是通过使用表3 中的参数,在所提出的 LTSpice 仿真器模型上施加 1.2 伏非晶化脉冲,随后施加 0.8 伏结晶脉冲,并记录单元两端的电学特性而获得的。另一方面,为了获得仿真器的实验结果,采用 0.35 微米 NMOS 技术以及列于表3 中的其他现成组件构建了仿真电路。然后施加非晶化和结晶脉冲,并对所构建的仿真电路的电学行为进行了测试。

从 Tcell 基于传热方程的计算 (2) 可以看出,当 Vin=0.8 V 和 Vin=1.2 V 时,Tcell 分别落在目标晶化和熔化温度范围内。因此,选择这些作为编程电压。计算还得出,读取电压必须低于 0.5V,以避免将单元的温度升高到编程水平。

4.1. 热模块电路

为了测试设计的电路,施加了电压范围(0.4−1.4 V),步长为 0.1V,并记录了设计的仿真器在仿真和实验装置中获得的 Tcell,并与从 (2) 式计算的 Tcell 进行了比较。需要注意的是,基于仿真器的 Tcell 和计算的 T 均遵循相同的指数趋势,如图12所示,这是由于在仿真电路设计中使用了二极管所致。

此外,由于设计的温度电路中表示 T 的电压当量 cell,通过曲线拟合 (4) 获得了计算的 Tcell 与仿真器结果之间的线性关系。因此,可通过测量 Tcell 节点处的电压并应用公式(4) 来计算摄氏度下的实际温度。同样,该方程也被用于测量结晶和熔化温度的电压当量,以便在控制模块中用作参考。

$$ T_{C}(°) = 2684.6(V_{cell}) + 207.42 $$ (4)

4.2. 决策模块电路

所设计的决策模块针对相变存储单元的三种主要操作进行了测试,即编程为 0(复位)、编程为 1(置位)和读取。该测试在仿真和实验装置中均进行。结果表明,信号符合表1中的逻辑预期值。逻辑零的范围为 −6 V,而逻辑一约为 1 V,如表2所示,这足以驱动后续模块和单元并提供正确的值。此外,需要注意的是仿真电路的实验结果一致。

| V (Tcell) | TcellTmelt(V) | TcellTcryst(V) | O1(V) | O2(V) |

|---|---|---|---|---|

| Sim | Exp | Sim | Exp | Sim |

| 1.2 | −8.816 | −6.8 | −8.816 | −6.8 |

| 0.8 | +0.887 | 1.08 | −8.816 | −6.8 |

| 0.1–0.4 | +0.878 | 0.76 | +0.891 | 0.800 |

表2 设计的判决电路的实验数据(Exp)和仿真结果(Sim)。

4.3. 控制模块电路

为了测试所设计的控制电路和前级存储单元的行为;施加了一系列编程和读取脉冲(Vin)。首先是一个结晶脉冲(Tp1),接着是读取脉冲(Tr1),然后是一个非晶化脉冲(Tp2),再接着是读取脉冲(Tr2),如图13所示。在此模块中,展示了电路模块与单元信号之间的互连。注意到所设计的存储单元在测试持续时间内保持了先前编程状态(Q)的完整性,从而在整个测试期间阈值电压呈现出正确的逻辑值。此外,编程信号 Vprog/read 直接取决于当前阈值与输入信号的比较结果。在前级电路提供正确信号的情况下,Vprog/read 符合预期结果,如图13所示。

4.4. 电流‐电压特性 & 电阻模块电路

为了获得设计的仿真电路所表现出的电流‐电压特性,向单元施加范围为(0.1–1.4 V)的递增电压脉冲,一次从高阻态初始状态开始,另一次从低阻态初始状态开始。然后测量通过 Rtest 和 PCM 单元等效电阻的相应电流。

设计的仿真电路成功展示了复位过程中出现的负阻行为和电阻下降,如图14所示。此外,来自仿真和实验测试电路的模拟 I‐V 曲线,以及实际 PCM 单元的实验获得曲线(图14)具有很好的一致性,从而验证了所提出的仿真器设计。

此外,对于在图13中施加的相同脉冲序列,测量了通过 Rtest 的电流,并将施加电压除以电流以获得存储单元的电阻。如图15所示,存储单元的电阻符合预期,表明电阻模块中的 NMOS 开关正常工作。因此证明,通过正确的控制信号,设计的仿真器能够提供准确的电阻水平。

5. 结论

仿真电路是相变存储器应用开发与优化过程中不可或缺的设计与研究工具。本文借助 SPICE 工具(LTSpice)设计了一种 PCM 存储单元模拟器,并仅采用分立式现成电子元件进行搭建。

对基于 GST 的 PCM 单元在仿真环境中并通过构建电路对所提出的模型进行了测试。发现该模型能够模拟相变存储单元对外部施加电压的电学特性响应。该仿真器能够生成相变存储单元的温度分布,并展示电阻依赖对施加脉冲的响应,并重现相变存储器标准的 I‐V 特性。仿真和实验装置的结果一致,且与实际的相变存储器单元的实验获得结果高度吻合[28]。因此,验证了设计的仿真器的可行性,并确认了该模型具有类似 PCM 的行为,使其适用于研究相变存储器的电学行为,并作为探索可能的 PCM 应用的平台。

本文提出的仿真电路采用 0.35 微米工艺构建,代表了一个单比特存储相变存储器单元。所提出的仿真电路设计可以通过简单调整参考值(如 RSET、RRESET、RON、Vthmin 和 Vthmax)来轻松适配任何材料类型或器件尺寸。由于操作原理保持不变,因此该模型可用于不同 PCM 器件材料和尺寸。然而,在后续工作中,将研究工艺节点和多比特存储对所提 出仿真电路性能的影响。此外,未来的工作还将致力于提高所用实验装置的分辨率,使其超过当前的 0.1 伏特,以捕捉在 (0.78 V) 发生的阈值开关现象。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)