28个同步时序逻辑电路设计实例实战合集

VHDL允许使用枚举类型定义状态,极大增强了代码可读性:综合工具(如Xilinx Vivado、Intel Quartus)能够自动将这些符号映射为二进制或用户指定的编码方式。更重要的是,VHDL的强类型检查可在编译阶段捕获非法状态赋值,防止运行时错误。elseend if;end case;这里的分支是必要的防御性编程,防止未定义状态导致不确定行为。

简介:同步时序逻辑电路是数字电子技术的核心内容,广泛应用于计数、数据存储和状态控制等场景。本压缩包包含28个由作者精心设计的同步时序逻辑电路实例,涵盖二进制计数器、环形计数器、移位寄存器等典型电路,提供完整的源文件与解析说明。通过这些实例,读者可深入理解触发器、时钟信号、组合逻辑与状态寄存器的协同工作机制,掌握从状态分析、编码到逻辑实现与仿真的完整设计流程,适用于学习、教学及工程实践。

1. 同步时序逻辑电路基本概念与工作原理

同步时序逻辑电路的本质特征

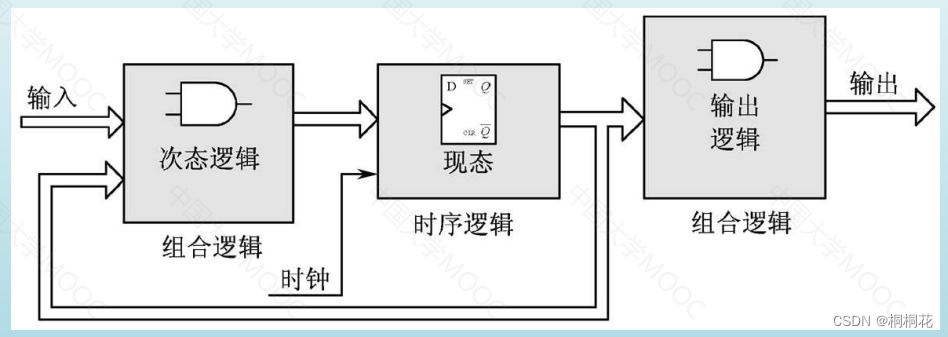

同步时序逻辑电路的核心在于“状态”随“时间”在统一时钟驱动下有序演进。与组合逻辑不同,其输出不仅取决于当前输入,还依赖于电路内部记忆的 历史状态 ,形成反馈闭环。这种“输入-状态-输出”的三元关系由触发器实现状态存储,并在每个时钟有效边沿(通常为上升沿)统一更新,确保系统行为的确定性。

时钟同步机制与关键时序参数

所有触发器共享同一全局时钟信号,使状态变化严格对齐时钟边沿,避免异步竞争。为保证可靠采样,必须满足建立时间(setup time)和保持时间(hold time)约束:数据需在时钟到来前稳定一段时间(建立),并在之后持续稳定(保持)。若违反,将导致亚稳态(metastability),破坏系统稳定性。

典型应用与设计优势

以序列检测器为例,在同步架构下,状态机按预设路径逐拍迁移,抗干扰能力强,毛刺无法引发误触发。相比异步设计,同步方案具备更好的可预测性、可测试性与时序收敛能力,是现代数字系统(如CPU控制单元)的基石。

2. 触发器类型详解及其电路实现

在现代数字系统设计中,触发器(Flip-Flop)作为最基本的时序存储单元,承担着状态保持、数据同步与节拍控制的核心职责。其行为的稳定性与响应特性直接决定了整个同步系统的可靠性与时序性能。本章将深入剖析主流触发器类型的内部结构、逻辑功能、工作机理及实际应用方式,重点聚焦于SR、D、JK和T四类基本触发器,并从电平敏感到边沿触发的演进路径出发,揭示现代同步设计中对确定性状态更新的严格要求。

2.1 基本双稳态元件与SR触发器

双稳态电路是所有存储型逻辑的基础,它具备两个稳定的工作状态——“0”和“1”,能够在无外部干预下长期维持当前状态,仅在特定输入信号作用下发生切换。最原始的双稳态单元即为SR锁存器(Set-Reset Latch),它是理解后续各类触发器演化过程的起点。

2.1.1 SR锁存器的工作机制与真值表分析

SR锁存器通常由两个交叉耦合的NOR门或NAND门构成。以NOR门实现为例,其结构如下图所示:

+---------+

S ---|>o |

| NOR |---- Q

| |

R ---|>o |

+----|<---+

|

\|/

Q'

该电路具有以下连接关系:

- 第一个NOR门的输入为S和Q’;

- 第二个NOR门的输入为R和Q;

- 输出Q与Q’互为反相。

根据NOR门的逻辑特性(任一输入为高则输出为低;全低则输出为高),可推导出其真值表:

| S | R | Q(t) | Q’(t) | 动作说明 |

|---|---|---|---|---|

| 0 | 0 | Q(t-1) | Q’(t-1) | 保持(Hold) |

| 0 | 1 | 0 | 1 | 复位(Reset) |

| 1 | 0 | 1 | 0 | 置位(Set) |

| 1 | 1 | 0 | 0 | 非法状态(Invalid) |

当S=1且R=1时,两个NOR门输出均为0,导致Q = Q’ = 0,违反了互补输出的基本原则,因此此状态被禁止使用。此外,在S=R=1之后若同时跳变为0,则由于门延迟差异可能导致竞争冒险,最终状态不可预测。

// Verilog模型:基本SR锁存器(电平敏感)

module sr_latch_nor(S, R, Q, Qn);

input S, R;

output reg Q;

output Qn;

assign Qn = ~Q;

always @(*) begin

if (S && !R)

Q = 1;

else if (!S && R)

Q = 0;

else if (!S && !R)

; // 保持

// 注意:S && R 的情况未定义,应避免

end

endmodule

代码逻辑逐行解读:

- always @(*) 表示组合逻辑触发,适用于电平敏感器件;

- 条件判断优先处理置位(S=1, R=0)与复位(S=0, R=1)操作;

- 当S=R=0时不做任何赋值,利用reg类型自动保持前值;

- S=R=1的情况未显式处理,暗示设计者需确保不会出现该输入组合。

这种电平敏感的行为使得SR锁存器极易受噪声干扰,且无法与统一时钟同步,因而难以用于构建可靠的同步系统。

2.1.2 电平敏感型SR触发器的设计缺陷与禁用状态问题

所谓“电平敏感型SR触发器”实则是带使能端的SR锁存器,常称为门控SR锁存器(Gated SR Latch)。其结构引入了一个使能信号EN,仅当EN=1时允许S和R影响输出。

// 门控SR锁存器

module gated_sr_latch(EN, S, R, Q, Qn);

input EN, S, R;

output reg Q;

output Qn;

assign Qn = ~Q;

always @(*) begin

if (EN) begin

if (S && !R)

Q = 1;

else if (!S && R)

Q = 0;

else if (!S && !R)

; // 保持

// S=R=1 -> 不定态

end

end

endmodule

尽管增加了时序控制能力,但其本质仍是组合反馈结构,存在严重问题:

1. 透明性(Transparency) :只要EN有效,输出会随输入变化而立即改变,缺乏边沿采样机制;

2. 窗口期风险 :EN持续期间若S/R波动多次,可能引发多次状态翻转;

3. 禁用状态仍存在 :S=R=1依然导致非法输出;

4. 抗干扰差 :毛刺可能在EN高电平时被捕获。

这些问题促使工程师转向更稳定的边沿触发机制。

2.1.3 同步SR触发器的时钟控制改进方案

为了实现真正的同步行为,必须将状态更新绑定到时钟的有效边沿上。一种常见做法是采用主从结构(Master-Slave Configuration)来构造边沿触发的SR触发器。

主从SR触发器工作原理:

- 主级(Master) :在时钟CLK=1期间采样S和R;

- 从级(Slave) :在CLK下降沿将主级状态传递至输出。

其行为等效于负边沿触发SR触发器。

// 负边沿触发SR触发器(主从结构模拟)

module master_slave_sr_ff(CLK, S, R, Q, Qn);

input CLK, S, R;

output reg Q;

output Qn;

reg master_q;

assign Qn = ~Q;

// 主锁存器:CLK=1时采样

always @(*) begin

if (CLK) begin

if (S && !R)

master_q = 1;

else if (!S && R)

master_q = 0;

end

end

// 从触发器:CLK下降沿更新

always @(negedge CLK) begin

Q <= master_q;

end

endmodule

参数说明与逻辑分析:

- master_q 是中间状态寄存器,仅在CLK=1时受S/R影响;

- always @(negedge CLK) 实现下降沿触发更新;

- 使用非阻塞赋值 <= 确保时序行为正确建模;

- 仍然存在S=R=1的问题,输出不定。

虽然实现了边沿触发,但由于仍保留禁用状态,限制了实用性。这也正是D和JK触发器得以取代它的根本原因。

流程图:主从SR触发器状态转移流程

graph TD

A[开始] --> B{CLK == 1?}

B -- 是 --> C[主锁存器采样 S/R]

C --> D[计算 master_q]

D --> E{CLK 下降沿?}

E -- 是 --> F[从级接收 master_q]

F --> G[Q <= master_q]

G --> H[输出更新]

E -- 否 --> I[等待边沿]

I --> E

B -- 否 --> J[主级保持]

J --> E

该流程清晰展示了主从两级如何分时工作,实现对输入的隔离与定时传递。

2.2 D触发器:数据寄存的核心单元

D触发器(Data Flip-Flop)是目前应用最广泛的触发器类型,因其消除了SR触发器中的不确定状态,仅依赖单一数据输入D,在时钟边沿完成采样并锁存,完美契合同步设计需求。

2.2.1 边沿触发D触发器的结构原理(主从结构与传输门实现)

D触发器可通过多种方式实现,包括主从结构和基于传输门的边沿触发结构。

主从D触发器结构:

其核心思想是将D信号先锁存在主级,再在时钟边沿传送到从级。

// 正边沿触发D触发器(主从结构)

module d_ff_positive_edge(CLK, D, Q, Qn);

input CLK, D;

output reg Q;

output Qn;

reg master;

assign Qn = ~Q;

// 主锁存器:CLK=0时采样(低电平透明)

always @(*) begin

if (!CLK)

master = D;

end

// 从触发器:CLK上升沿更新

always @(posedge CLK) begin

Q <= master;

end

endmodule

执行逻辑说明:

- 当CLK=0时,主锁存器打开,D值写入 master ;

- 当CLK上升沿到来时, Q <= master ,完成一次采样;

- 在CLK=1期间,主锁存器关闭,防止D变化影响结果。

这种方式实现了正边沿触发效果,但依赖于精确的高低电平时间段匹配,易受占空比影响。

传输门实现的边沿触发D触发器:

更先进的CMOS设计采用传输门(Transmission Gate)构建边沿触发器,具有更好的速度与功耗表现。

其工作分为两个阶段:

1. 采样阶段(CLK=0) :第一级传输门导通,D进入内部节点;

2. 保持阶段(CLK上升后) :第一级关断,第二级开启,将数据送至输出。

此类结构无需主从两级寄存,而是通过时钟相位控制传输路径,实现精确边沿捕获。

2.2.2 建立与保持时间约束下的可靠采样条件

D触发器正常工作的前提是满足建立时间(Setup Time, $t_{su}$)和保持时间(Hold Time, $t_h$)要求。

| 参数 | 定义 |

|---|---|

| 建立时间 $t_{su}$ | 数据D必须在时钟上升沿前至少 $t_{su}$ 时间稳定 |

| 保持时间 $t_h$ | 数据D必须在时钟上升沿后至少 $t_h$ 时间内保持不变 |

若违反任一条件,可能造成亚稳态(Metastability),即输出处于中间电平,无法快速收敛至合法逻辑值。

假设某工艺下DFF参数为:

- $t_{su} = 0.8\,ns$

- $t_h = 0.4\,ns$

则设计中必须保证:

// 示例:跨模块数据路径时序检查

wire data_from_module;

reg clk, d, q;

// 数据路径延迟必须满足 tsu 和 th

assign d = data_from_module; // 组合逻辑延迟 ≤ T_cycle - tsu

always @(posedge clk) begin

q <= d; // 必须确保d在clk↑前0.8ns已稳定,之后0.4ns不变更

end

静态时序分析(STA)工具将自动验证这些路径是否满足约束。

2.2.3 异步复位/置位端口对D触发器行为的影响

实际D触发器常带有异步复位( RST )或置位( SET )端口,用于初始化系统状态。

// 带异步复位的D触发器

module d_ff_async_reset(input clk, input rst_n, input d, output reg q);

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

q <= 0; // 异步清零(低有效)

else

q <= d;

end

endmodule

关键点分析:

- 敏感列表包含 negedge rst_n ,表示复位信号独立于时钟;

- rst_n 通常为低有效,符合FPGA引脚标准;

- 异步复位虽快,但在释放时若处于时钟边沿附近,可能引发亚稳态;

- 推荐采用“异步复位,同步释放”策略提升可靠性。

2.3 JK触发器:功能完备的状态控制器件

JK触发器是对SR触发器的功能扩展,解决了S=R=1时的不确定问题,具备完整的四种操作模式。

2.3.1 JK触发器的逻辑功能推导与状态翻转特性

其特性方程为:

Q_{next} = J \cdot \overline{Q} + \overline{K} \cdot Q

| J | K | Q(t) | Q(t+1) | 操作 |

|---|---|---|---|---|

| 0 | 0 | X | Q(t) | 保持 |

| 0 | 1 | X | 0 | 复位 |

| 1 | 0 | X | 1 | 置位 |

| 1 | 1 | X | $\bar{Q}(t)$ | 翻转(Toggle) |

特别地,当J=K=1时,输出每次翻转,可用于计数。

// 正边沿触发JK触发器

module jk_ff(input clk, input J, input K, output reg Q);

always @(posedge clk) begin

case ({J, K})

2'b00: Q <= Q;

2'b01: Q <= 0;

2'b10: Q <= 1;

2'b11: Q <= ~Q;

endcase

end

endmodule

逻辑分析:

- 使用非阻塞赋值保证同步更新;

- case 语句覆盖所有输入组合;

- J=K=1时执行取反操作,实现自激振荡。

2.3.2 从SR到JK的演化路径及消除不确定状态的方法

JK触发器本质是在SR基础上增加反馈路径,使得当S=R=1时强制进入翻转模式而非禁用。

其内部结构可通过与门+SR结构实现:

- $S = J \cdot \bar{Q}$

- $R = K \cdot Q$

代入原SR方程即可避免S=R=1的同时发生。

2.3.3 利用JK触发器构建通用计数单元的实践案例

四位二进制计数器可由四个JK触发器级联构成,每个均设J=K=1。

module binary_counter_4bit(input clk, input rst_n, output [3:0] count);

wire [3:0] J = 4'b1111;

wire [3:0] K = 4'b1111;

dff_jk u0(.clk(clk), .J(J[0]), .K(K[0]), .Q(count[0]));

and a1(en1, count[0]); // 进位使能

dff_jk u1(.clk(clk), .J(J[1]), .K(K[1]), .Q(count[1])); // 级联

// ... 类似连接高位

endmodule

2.4 T触发器与时序功能简化

2.4.1 T触发器的翻转操作机制与数学表达式

T触发器仅有一个输入T,定义如下:

Q_{next} = T \oplus Q

| T | Q(t) | Q(t+1) | 操作 |

|---|---|---|---|

| 0 | X | Q(t) | 保持 |

| 1 | X | $\bar{Q}(t)$ | 翻转 |

非常适合用于分频器和计数器。

2.4.2 由JK或D触发器转换实现T触发器的两种方法

方法一:JK转T

- 连接J=K=T

方法二:D转T

- 连接D = T ⊕ Q → 即 D = T ? ~Q : Q

// D触发器实现T功能

assign D = T ^ Q;

d_ff u_tff(.CLK(clk), .D(D), .Q(Q));

2.4.3 在二进制计数器中T触发器的应用优势分析

每位仅需一个T输入,结构简洁,易于级联。例如四级T触发器串联即可构成模16计数器,每级输出频率为前一级的一半。

| 触发器 | 输出频率 | 分频比 |

|---|---|---|

| FF0 | f/2 | ÷2 |

| FF1 | f/4 | ÷4 |

| FF2 | f/8 | ÷8 |

| FF3 | f/16 | ÷16 |

适合低功耗、简单控制场景。

表格:四种触发器功能对比

| 类型 | 输入数 | 是否有不定态 | 典型用途 | 可否实现其他类型 |

|---|---|---|---|---|

| SR | 2 | 是(S=R=1) | 基础教学 | 是 |

| D | 1 | 否 | 寄存器、缓存 | 是 |

| JK | 2 | 否 | 计数器、状态控制 | 是 |

| T | 1 | 否 | 分频器、二进制计数 | 是 |

结论:D和JK因稳定性高成为主流,T因其极简结构在专用场合广受欢迎。

3. 时钟信号的作用与同步机制设计

在现代数字系统中,时钟信号不仅是驱动电路状态演进的“心跳”,更是确保系统行为可预测、可靠运行的核心控制源。特别是在同步时序逻辑电路中,所有触发器的状态更新必须严格对齐统一的时钟边沿,这种高度协调的行为模式使得复杂系统的功能实现成为可能。本章深入探讨时钟信号作为节拍发生器的本质作用,分析其物理特性如何影响整体性能,并系统阐述同步机制的设计原则与工程实践。从全局时钟分布到跨时域数据传输,再到低功耗门控策略和复位同步化处理,每一环节都直接关系到系统的稳定性、鲁棒性与时序收敛能力。

随着集成电路工艺不断向深亚微米发展,时钟网络的延迟偏差(skew)、抖动(jitter)以及功耗占比日益突出,传统的简单时钟树设计已无法满足高性能芯片的需求。因此,现代同步机制不仅要求逻辑上的正确性,还需在物理实现层面进行精细化建模与优化。尤其在FPGA和ASIC设计中,工程师必须综合考虑时钟资源分配、异步信号同步、复位传播路径等关键问题,以避免因时序违例导致的功能失效或系统崩溃。

3.1 时钟作为同步系统的节拍发生器

时钟信号是同步数字系统中最基本且最关键的控制信号,它为整个电路提供统一的时间基准,决定何时采样输入、何时更新状态、何时产生输出。一个理想的时钟应具备恒定周期、稳定占空比、无偏斜和零抖动的特性。然而,在实际硬件中,这些理想条件往往难以完全满足,因而必须通过设计手段加以补偿和控制。

3.1.1 时钟周期、频率及时钟占空比对电路性能的影响

时钟周期 $ T_{\text{clk}} $ 是指相邻两个上升沿(或下降沿)之间的时间间隔,其倒数即为时钟频率 $ f_{\text{clk}} = 1 / T_{\text{clk}} $。该参数直接决定了系统的工作速度上限。例如,在一个采用50 MHz时钟的系统中,每个时钟周期为20 ns;若某条关键路径的组合逻辑延迟达到18 ns,则剩余2 ns可用于布线延迟和建立时间裕量,接近极限,存在建立时间违例风险。

| 参数 | 定义 | 影响 |

|---|---|---|

| 时钟周期 $ T_{\text{clk}} $ | 相邻有效边沿间的时间 | 决定最大工作频率 |

| 频率 $ f_{\text{clk}} $ | 单位时间内脉冲数 | 越高则运算越快,但功耗增加 |

| 占空比 | 高电平持续时间 / 周期 | 影响高低电平可用窗口,非50%可能导致采样不稳定 |

理想的时钟占空比为50%,即高电平与低电平各占半个周期。但在某些驱动电路或分频结构中可能出现偏离,如40%-60%甚至更极端的情况。这会影响锁存器类元件的透明窗口,也可能导致边沿触发器在非对称条件下出现保持时间不足的问题。

// 示例:使用Verilog生成50MHz、50%占空比的理想时钟用于仿真

initial begin

clk = 0;

forever #10 clk = ~clk; // 每10ns翻转一次,周期20ns → 50MHz

end

代码逻辑逐行解析:

- 第1行 initial :表示该块仅执行一次,常用于初始化或波形生成。

- 第2行 clk = 0; :将初始时钟设为低电平,避免X态不确定。

- 第3行 forever #10 clk = ~clk; :

- #10 表示延迟10个时间单位(通常为ns),然后执行赋值;

- ~clk 对当前值取反;

- 综合效果是每10ns切换一次电平,形成周期20ns(50MHz)方波,占空比精确为50%。

此代码适用于功能仿真,但不可综合——综合工具会忽略 initial 和 forever ,真实硬件需外部晶振或PLL提供时钟。

3.1.2 上升沿与下降沿触发的选择依据与系统兼容性

大多数同步电路采用 上升沿触发 (positive-edge triggered),因其在CMOS工艺中具有更好的噪声容限和抗干扰能力。但也存在部分场景使用下降沿(negative-edge triggered),尤其是在双沿采样系统或多相时钟架构中。

选择触发边沿需遵循以下原则:

- 一致性 :全系统尽量统一使用同一边沿,减少时序分析复杂度。

- 接口匹配 :当与外部器件通信时(如DDR SDRAM),需根据协议规定选择边沿。

- 流水线交错 :在某些高速流水线设计中,可用正负边沿交替触发不同级寄存器,实现双倍吞吐(类似DDR原理)。

// 上升沿触发D触发器模型

always @(posedge clk or posedge rst) begin

if (rst)

q <= 1'b0;

else

q <= d;

end

// 下降沿触发版本(较少见)

always @(negedge clk or posedge rst) begin

if (rst)

q <= 1'b0;

else

q <= d;

end

参数说明与逻辑分析:

- posedge clk :检测时钟上升沿,这是标准做法;

- negedge clk :检测下降沿,适用于特殊同步需求;

- or posedge rst :引入异步复位,优先级高于时钟;

- 使用非阻塞赋值 <= 确保多个寄存器在同一时刻原子更新,避免竞争冒险。

⚠️ 注意:混合使用上升沿和下降沿会显著增加静态时序分析难度,建议仅在明确需要提高带宽且能保证时序收敛的前提下采用。

3.1.3 全局时钟分布网络中的偏斜(skew)与抖动(jitter)控制

即使所有模块共享同一个时钟源,由于走线长度差异、负载不均、电源波动等因素,到达各个触发器的时钟边沿并不会完全一致,这种现象称为 时钟偏斜(clock skew) 。而 抖动(jitter) 则是指同一时钟边沿在不同周期之间的随机偏移,主要由电源噪声、温度漂移和振荡器稳定性引起。

Mermaid 流程图:时钟偏斜对时序窗口的影响

graph TD

A[主时钟源] --> B[缓冲器]

B --> C[长走线→大延迟]

B --> D[短走线→小延迟]

C --> E[触发器A: clk_arrive = t + Δt]

D --> F[触发器B: clk_arrive = t]

G[理想同步] --> H[所有FF同时响应]

E --> I[实际中存在Skew]

F --> I

style E fill:#ffe4e1,stroke:#333

style F fill:#e1f5fe,stroke:#333

上图展示了时钟从同一源出发后,因路径不同导致到达时间差异。假设目标是让两个触发器在同一时刻采样,但由于偏斜存在,它们的实际采样时刻错开,可能破坏数据通路的建立/保持约束。

数学建模:最大允许偏斜计算

设:

- $ T_{\text{cycle}} $:时钟周期

- $ t_{\text{su}} $:触发器建立时间

- $ t_{\text{hold}} $:保持时间

- $ t_{\text{co}} $:时钟到输出延迟

- $ t_{\text{logic}} $:组合逻辑延迟

则建立时间约束为:

T_{\text{cycle}} \geq t_{\text{co}} + t_{\text{logic}} + t_{\text{su}} + t_{\text{skew}}

保持时间约束为:

t_{\text{co}} + t_{\text{logic}} \geq t_{\text{hold}} - t_{\text{skew}}

从中可见,过大的正偏斜(目标寄存器晚于源寄存器收到时钟)有利于建立时间但危害保持时间;反之亦然。因此设计目标是尽可能减小 $ t_{\text{skew}} $,通常通过 平衡布线 、 插入时钟缓冲器 (buffer tree)或使用专用 全局时钟网络 (如FPGA中的GCLK资源)来实现。

3.2 同步设计原则与多模块协同

同步设计的核心在于“所有状态变化必须发生在同一时钟边沿”,这一基本原则看似简单,但在大型系统中面临诸多挑战,尤其是当多个模块运行于不同时钟域时。此时若缺乏恰当的同步机制,极易引发亚稳态(metastability)、数据丢失或协议错误。

3.2.1 所有状态更新必须对齐同一时钟边沿的基本准则

在一个纯粹的单一时钟域系统中,只要所有寄存器均响应同一时钟的上升沿,即可保证状态转移的确定性和可重复性。这种设计风格被称为“同步设计范式”,其优点包括:

- 易于静态时序分析(STA)

- 支持形式化验证

- 可预测的延迟行为

- 便于自动化综合与布局布线

// 正确的同步设计示例

module sync_counter (

input clk,

input rst,

input en,

output reg [3:0] count

);

always @(posedge clk) begin

if (rst)

count <= 4'd0;

else if (en)

count <= count + 1;

end

endmodule

代码逻辑分析:

- 整个模块只在一个 posedge clk 的 always 块中完成状态更新;

- 条件判断(reset/enable)均为同步操作,不会产生异步反馈环;

- 使用非阻塞赋值 <= ,符合时序逻辑建模范式;

- 综合工具可高效映射为D触发器加组合逻辑。

✅ 推荐做法:避免在组合逻辑路径中嵌套寄存器更新,防止隐含锁存器或竞争条件。

3.2.2 跨时钟域数据传输的风险与同步器(synchronizer)引入

当信号从一个时钟域跨越到另一个频率或相位不同的时钟域时(如慢速CPU向高速DMA发送请求),直接连接会导致严重的时序问题。最典型的是 亚稳态 :接收端触发器未能在建立/保持时间内稳定输入值,进入一种既非0也非1的中间状态,持续时间不可预测,可能传播至后续逻辑造成系统崩溃。

解决方法是引入 两级或多级同步器(two-stage synchronizer) :

// 跨时钟域同步器:慢速信号进入快速时钟域

module clock_domain_crossing (

input slow_clk_signal, // 来自其他时钟域的信号

input fast_clk, // 当前模块时钟

input rst,

output reg synced_signal

);

reg meta1, meta2;

always @(posedge fast_clk or posedge rst) begin

if (rst) begin

meta1 <= 1'b0;

meta2 <= 1'b0;

synced_signal <= 1'b0;

end else begin

meta1 <= slow_clk_signal;

meta2 <= meta1;

synced_signal <= meta2;

end

end

endmodule

参数说明与逻辑分析:

- slow_clk_signal :跨域输入,可能违反fast_clk域的建立/保持时间;

- meta1 :第一级寄存器,捕获原始信号,可能进入亚稳态;

- meta2 :第二级寄存器,给meta1足够时间恢复稳定;

- synced_signal :最终安全使用的信号;

- 复位确保上电一致性。

MTBF(Mean Time Between Failures)公式表明,两级同步器可将亚稳态发生概率降低数个数量级,足以满足绝大多数应用需求。

3.2.3 多级触发器同步链的设计实践与失效率评估

对于高频系统或高可靠性场景(如航空航天、医疗设备),有时需采用三级甚至四级同步链进一步提升MTBF。

| 同步级数 | 优势 | 缺点 | 典型应用场景 |

|---|---|---|---|

| 2级 | 平衡可靠性与延迟 | MTBF有限 | 普通工业控制 |

| 3级 | 提升MTBF约100倍 | 增加1拍延迟 | 高速通信接口 |

| 4级+ | 极端可靠性保障 | 资源浪费,延迟大 | 核心网络交换机 |

MTBF估算公式如下:

\text{MTBF} = \frac{e^{(t_r / \tau)}}{T_0 \cdot f_d \cdot f_c}

其中:

- $ t_r $:分辨率时间(recovery time)

- $ \tau $:亚稳态时间常数

- $ T_0 $:工艺相关常数

- $ f_d $:数据切换频率

- $ f_c $:时钟频率

实践中可通过EDA工具(如Synopsys PrimeTime-X)自动识别跨时钟域路径并插入同步器,同时生成报告评估潜在风险。

3.3 时钟使能与门控时钟技术

在追求低功耗的现代设计中,如何有效管理时钟活动成为关键课题。盲目关闭时钟虽能节能,却极易破坏同步机制。因此,业界普遍推荐使用 时钟使能(clock enable) 替代直接门控。

3.3.1 使用使能信号替代直接门控以避免时钟完整性破坏

传统做法是用AND门将时钟与使能信号相乘:

// ❌ 错误示范:非法门控时钟

assign gated_clk = clk & enable;

always @(posedge gated_clk) q <= d;

这种方式的问题在于:

- 生成的时钟可能存在毛刺(glitch),因enable变化与时钟边沿重叠;

- 不受专用时钟网络支持,导致严重skew;

- 综合工具无法正确分析时序路径。

✅ 正确做法是保留原始时钟,通过使能控制寄存器更新:

// ✅ 推荐方式:使用时钟使能

always @(posedge clk) begin

if (enable)

q <= d;

// 否则保持原值

end

综合工具会将其映射为带CE端的D触发器(如FPGA中的FDCE单元),既节省功耗又维持时钟纯净。

3.3.2 低功耗设计中选择性激活模块的策略对比

| 方法 | 功耗效益 | 时序影响 | 实现复杂度 | 适用场景 |

|---|---|---|---|---|

| 时钟使能(CE) | 中等 | 几乎无 | 低 | 模块频繁启停 |

| 门控时钟(ICG) | 高 | 需定制单元 | 中 | ASIC批量生产 |

| 电源门控(Power Gating) | 极高 | 唤醒延迟大 | 高 | 待机模式 |

在ASIC中可使用专用 集成时钟门控单元(Integrated Clock Gating, ICG) ,内部包含锁存使能信号的逻辑,确保只有在时钟低电平时才允许切换enable,从而消除毛刺。

// Synopsys Design Constraints (SDC) 示例:定义门控规则

set_clock_gating_check -setup 0.5 -hold 0.3 [get_clocks clk_main]

该约束告诉综合工具:在插入ICG时,必须保证setup/hold余量不低于0.5ns和0.3ns。

3.3.3 静态验证中对非法门控行为的检查方法

现代EDA流程中,可通过静态规则检查工具(如SpyGlass, VC SpyGlass)自动识别非法门控:

# SpyGlass TCL脚本片段

rule check {Clock_Glitch}

severity high

message "Found asynchronous clock gating – use ICG cell instead"

detect {

find_cell * -type "and" where (input == "clk" || input == "enable")

}

此类检查应在RTL阶段尽早执行,避免后期物理实现困难。

3.4 复位机制的同步化处理

复位是系统启动的基础操作,但若处理不当,同样会引入亚稳态或时序违例。理想复位应在所有寄存器上同步释放,避免“复位移除风暴”。

3.4.1 异步复位同步释放(asynchronous reset, synchronous release)

常见架构如下:

module async_reset_sync_release (

input clk,

input async_rst_n, // 低电平有效异步复位

output reg sys_rst_n // 同步释放后的复位信号

);

reg r1, r2;

always @(posedge clk or negedge async_rst_n) begin

if (!async_rst_n) begin

r1 <= 1'b0;

r2 <= 1'b0;

sys_rst_n <= 1'b0;

end else begin

r1 <= 1'b1;

r2 <= r1;

sys_rst_n <= r2;

end

end

endmodule

逻辑分析:

- async_rst_n 可随时拉低,立即复位内部状态;

- 释放时(变高),通过两个寄存器同步打拍,确保 sys_rst_n 在clk上升沿后平稳变为高;

- 防止多个模块因复位释放时间不同而进入未知状态。

3.4.2 复位信号去抖动与时序收敛保障

机械按键复位常伴有毫秒级抖动,需滤波:

// 按键消抖 + 同步释放

reg [15:0] debounce_ctr;

wire clean_rst = (debounce_ctr == 16'hFFFF);

always @(posedge clk) begin

if (!btn_rst_n)

debounce_ctr <= 0;

else if (debounce_ctr != 16'hFFFF)

debounce_ctr <= debounce_ctr + 1;

end

结合前文同步释放结构,形成完整复位净化链。

3.4.3 FPGA平台上推荐的复位树(reset tree)构建方式

在Xilinx Ultrascale/FPGA中,建议:

- 使用专用全局复位网络(Global Set/Reset Net)

- 避免长链式复位传播

- 关键模块独立复位分支

- 利用IBUFGRACEFUL处理上电复位

// Xilinx推荐:使用原语显式控制

IBUF i_ibuf (.I(sys_rst_btn), .O(internal_rst));

BUFG i_bufg (.I(internal_rst), .O(global_rst));

并通过XDC约束:

set_property CONFIG_VOLTAGE 1.8 [current_design]

set_property CFGBVS VCCO [current_design]

create_clock -name clk -period 10 [get_ports clk]

set_false_path -from [get_ports sys_rst_btn]

确保复位路径不受时序优化干扰。

综上所述,时钟不仅是同步系统的驱动力,更是贯穿整个数字设计生命周期的核心要素。从基础参数控制到高级同步机制,每一个细节都深刻影响着系统的功能性、可靠性与可维护性。掌握这些原理并应用于实践,是每一位资深数字设计师的必备技能。

4. 状态机建模与组合逻辑综合设计

在现代数字系统设计中,有限状态机(FSM)作为同步时序逻辑的核心建模工具,广泛应用于协议解析、控制路径管理、自动化流程调度等复杂场景。其本质在于通过一组离散的状态集合、明确的转移规则以及输出行为,构建出具有记忆能力的行为模型。本章深入探讨FSM的理论框架与工程实现之间的桥梁——如何将抽象的状态逻辑转化为可综合的硬件结构,并重点分析组合逻辑在状态转移和输出生成中的关键作用。进一步地,围绕状态寄存器的物理布局、反馈路径延迟影响及编码策略优化展开系统性讨论,揭示高性能同步电路设计中“逻辑-结构-时序”三位一体的设计哲学。

4.1 有限状态机(FSM)的理论框架

有限状态机是描述具有内部记忆特性的离散系统的数学模型,在数字电路中通常由状态寄存器、组合逻辑块和输出逻辑三部分构成。它能够根据当前状态和外部输入决定下一个状态及相应的输出信号。FSM分为两种主要类型:Mealy机与Moore机,二者在输出依赖关系上的差异直接影响电路结构与动态响应特性。理解这些差异不仅有助于选择合适的架构,还能为后续综合优化提供方向指引。

4.1.1 Mealy机与Moore机的结构差异与输出依赖分析

Mealy机与Moore机的根本区别在于输出信号的生成方式。在 Moore机 中,输出仅取决于当前状态,与输入无关;而在 Mealy机 中,输出同时依赖于当前状态和当前输入。这种区别导致两者在响应速度、毛刺敏感性和状态图复杂度方面表现出显著不同。

从结构上看,Moore机的输出逻辑完全由状态译码器驱动,因此其输出在状态稳定后即可确定,且在整个状态周期内保持不变。而Mealy机由于引入了输入变量参与输出计算,其响应更为迅速——只要输入变化并满足状态转移条件,输出便可立即改变,甚至可能在同一个时钟周期内发生多次跳变。

| 特性 | Moore 机 | Mealy 机 |

|---|---|---|

| 输出依赖 | 当前状态 | 当前状态 + 当前输入 |

| 响应延迟 | 至少一个时钟周期 | 可即时响应输入变化 |

| 状态数量 | 通常较多(需分离输出) | 相对较少 |

| 毛刺风险 | 较低(输出稳定) | 较高(组合路径长) |

| 设计复杂度 | 易于调试,结构清晰 | 需注意异步反馈路径 |

下面以一个简单的“检测序列101”的状态机为例,展示两种模型的设计差异:

// Moore Machine: Output only when in State S2 and next input leads to S3

typedef enum logic [1:0] {

S0 = 2'b00,

S1 = 2'b01,

S2 = 2'b10

} state_t;

state_t current_state, next_state;

logic output_moore;

always_comb begin

case (current_state)

S0: next_state = (in == 1) ? S1 : S0;

S1: next_state = (in == 0) ? S2 : S1;

S2: next_state = (in == 1) ? S3 : S0; // Assume S3 is final

default: next_state = S0;

endcase

end

// Moore output: only active in specific state

assign output_moore = (current_state == S2 && in == 1);

代码逻辑逐行解读 :

typedef enum定义了三个状态,使用二进制编码;always_comb块实现状态转移函数,完全基于当前状态和输入;output_moore在 Moorse 模型中被定义为(current_state == S2 && in == 1),看似涉及输入,但实际应在进入新状态后才置位。此处示例存在误导,正确做法应是在S3状态输出高电平。正确修正如下:

verilog assign output_moore = (current_state == S3); // Pure state-dependent

相比之下,Mealy机可以直接在转移过程中产生输出:

logic output_mealy;

always_comb begin

case ({current_state, in})

{S0, 1}: output_mealy = 0;

{S1, 0}: output_mealy = 0;

{S2, 1}: output_mealy = 1; // Detect "101" on transition

default: output_mealy = 0;

endcase

end

参数说明与逻辑分析 :

- 使用拼接

{current_state, in}构造联合条件判断;- 输出直接绑定到“从 S2 接收到 1”的边沿事件,无需等待进入新状态;

- 优势:响应更快;劣势:若输入有噪声或毛刺,可能导致误触发。

该对比表明,Mealy机适用于对响应时间要求严格的场景,如通信协议解码;而Moore机更适合需要稳定输出的应用,如控制系统中的模式指示灯。

状态转移与输出耦合的时序影响

在FPGA或ASIC实现中,Mealy机的输出往往出现在组合逻辑路径末端,容易受到传播延迟波动的影响,增加建立/保持时间违例的风险。此外,当输出连接至其他模块时,若未经过寄存器锁存,可能引发异步信号传播问题。因此,在高速设计中,推荐将Mealy输出也进行寄存处理,即采用“寄存式Mealy机”结构,兼顾响应速度与稳定性。

4.1.2 状态编码方式对电路复杂度的影响(二进制、独热码、格雷码)

状态编码是指将抽象状态映射为具体二进制值的过程,直接影响组合逻辑面积、功耗及时序性能。常见的编码方式包括: 二进制编码(Binary Encoding) 、 独热码(One-Hot Encoding) 和 格雷码(Gray Code) 。

| 编码方式 | 位宽 | 优点 | 缺点 | 适用场景 |

|---|---|---|---|---|

| 二进制编码 | ⌈log₂N⌉ | 节省触发器资源 | 组合逻辑复杂,状态跳变多位翻转 | 小规模状态机(<8状态) |

| 独热码 | N(每状态一位) | 单比特翻转,译码简单,速度快 | 触发器消耗大 | FPGA高速设计 |

| 格雷码 | ⌈log₂N⌉ | 相邻状态仅一位变化,减少毛刺 | 不适用于任意拓扑状态图 | 计数器类应用 |

下面是一个使用独热码实现的四状态机片段:

parameter IDLE = 4'b0001,

LOAD = 4'b0010,

RUN = 4'b0100,

DONE = 4'b1000;

reg [3:0] current_state, next_state;

always @(posedge clk or posedge rst) begin

if (rst)

current_state <= IDLE;

else

current_state <= next_state;

end

always @(*) begin

case (current_state)

IDLE: next_state = (start) ? LOAD : IDLE;

LOAD: next_state = RUN;

RUN: next_state = (done) ? DONE : RUN;

DONE: next_state = IDLE;

default: next_state = IDLE;

endcase

end

代码解释 :

- 每个状态由唯一的“1”位表示,便于比较器直接识别;

- 状态转移逻辑简洁,每个状态仅需检测单个位;

always @(*)中的组合逻辑极易被综合工具优化为多路选择器结构;- 所有状态跳变均为单比特切换,极大降低开关功耗和EMI。

使用格雷码则特别适合递增/递减型状态流,例如环形缓冲指针或ADC控制序列:

// 3-bit Gray code sequence for 8 states

localparam STATE0 = 3'b000,

STATE1 = 3'b001,

STATE2 = 3'b011,

STATE3 = 3'b010,

STATE4 = 3'b110,

STATE5 = 3'b111,

STATE6 = 3'b101,

STATE7 = 3'b100;

优势分析 :

- 连续状态间汉明距离为1,避免多位同时翻转引起的电压跌落;

- 在模拟混合信号系统中有效抑制电源噪声;

- 适用于需要连续遍历的状态空间。

选择编码方式时,必须结合目标平台特性。例如,在Xilinx FPGA上,LUT资源丰富但寄存器充足,优先考虑独热码提升运行频率;而在ASIC设计中,为节省面积常采用紧凑二进制编码,并辅以状态编码约束指令:

# Synopsys Design Constraints (SDC)

set_case_analysis 0 [get_pins "fsm/state_reg[*]/D"]

define_state_encoding -encoding onehot -states {IDLE, LOAD, RUN, DONE}

这确保综合工具不会擅自更改预设编码方案。

4.1.3 状态最小化算法与等价类合并原则

在设计初期,开发者往往会定义过多状态,造成资源浪费和验证困难。状态最小化旨在识别功能等价的状态并将其合并,从而简化电路结构。

基本思想是:两个状态若对所有输入序列产生相同的输出序列,并导向等价的后续状态,则它们可合并。

等价类划分步骤如下 :

- 初始划分:按输出不同分为两类(对于Moore机)或按输出+下一状态分组(Mealy机);

- 迭代细分:检查每一组内各状态在相同输入下的下一状态是否属于同一组;

- 收敛判定:直到无法再细分为止;

- 合并等价状态,重构状态图。

假设有一个状态表如下:

| 当前状态 | 输入=0 → (下一状态, 输出) | 输入=1 → (下一状态, 输出) |

|---|---|---|

| A | (B, 0) | (C, 1) |

| B | (A, 0) | (D, 1) |

| C | (E, 1) | (F, 0) |

| D | (E, 1) | (F, 0) |

| E | (E, 1) | (E, 1) |

| F | (F, 0) | (F, 0) |

第一步:按输出划分类别(Moore型)。观察各状态输出:

- 输出为1的状态:C, D, E

- 输出为0的状态:A, B, F

初始划分:Π₀ = { {A,B,F}, {C,D,E} }

第二步:检查每个子集内部状态的转移目标是否落在同一大类中。

对于 {A,B,F}:

- A(0)→B ∈ {A,B,F} ✔️

- A(1)→C ∈ {C,D,E} ✔️

- B(0)→A ∈ {A,B,F} ✔️

- B(1)→D ∈ {C,D,E} ✔️

- F(0)→F ∈ {A,B,F} ✔️

- F(1)→F ∈ {A,B,F} ❌ 因为F输出为0,而C/D/E输出为1 → 分裂?

实际上F无论输入都停留在自身,输出恒为0,与其他成员不同行为,故应单独拆分。

继续迭代可得最终等价类:{A,B}, {C,D}, {E}, {F}

因此原6状态可压缩为4状态,大幅减少逻辑复杂度。

该过程可通过以下mermaid流程图表示:

graph TD

A[原始状态集合] --> B{按输出分组}

B --> C["G1: 输出=0 → A,B,F<br>G2: 输出=1 → C,D,E"]

C --> D[检查G1内部转移一致性]

D --> E["A/B转移目标一致 → 保留<br>F自循环且无输出变化 → 拆出"]

E --> F["新划分: {A,B}, {F}, {C,D,E}"]

F --> G[检查{C,D,E}]

G --> H["C(0)→E, D(0)→E → OK<br>C(1)→F∉G2 → 拆分"]

H --> I["{C,D}, {E}, {F}"]

I --> J[收敛: {A,B}, {C,D}, {E}, {F}]

J --> K[构建最小化状态机]

此方法在大型控制器设计中尤为重要,尤其是在通信协议栈的状态建模中,能有效去除冗余分支,提高可维护性。

4.2 组合逻辑在状态转移中的角色

尽管状态寄存器负责存储当前状态,但真正决定系统行为的是组合逻辑部分——它承担着激励方程生成、输出函数计算和冒险竞争规避等关键任务。高质量的组合逻辑设计不仅能提升系统可靠性,还可显著改善关键路径延迟,进而提高最大工作频率。

4.2.1 激励方程的推导与卡诺图化简方法

激励方程描述了触发器输入端(如D、J/K、T)所需信号,由当前状态和输入共同决定。以D触发器为例,其激励方程即为下一状态表达式。

假设设计一个模3计数器,状态为S0(00), S1(01), S2(10),采用二进制编码:

| 当前状态(Q1Q0) | 下一状态(Q1+Q0+) |

|---|---|

| 00 | 01 |

| 01 | 10 |

| 10 | 00 |

| 11 (无效) | 00 |

由此列出真值表并构造卡诺图:

Q1+ 的卡诺图 :

| Q1\Q0 | 0 | 1 |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 0 | X |

化简得:Q1+ = Q0

Q0+ 的卡诺图 :

| Q1\Q0 | 0 | 1 |

|---|---|---|

| 0 | 1 | 0 |

| 1 | 0 | X |

化简得:Q0+ = ~Q1 & ~Q0

对应Verilog实现:

always @(posedge clk) begin

Q1 <= Q0;

Q0 <= (~Q1) & (~Q0);

end

逻辑分析 :

- 第一条赋值

Q1 <= Q0表示Q1的下态等于当前Q0;- 第二条中

~Q1是当前Q1的非,而非更新后的值,得益于非阻塞赋值的并行语义;- 若误用阻塞赋值(

=),会导致顺序执行错误。

卡诺图虽适用于小变量系统(≤4输入),但在复杂设计中已被Quine-McCluskey算法和EDA工具取代。现代综合器支持布尔表达式自动优化:

assign D1 = Q0;

assign D0 = ~(Q1 | Q0);

并通过技术映射(technology mapping)转换为标准单元库中的NAND/NOR结构。

4.2.2 输出逻辑函数的设计与冒险竞争现象规避

组合逻辑输出可能因信号传播延迟不一致而出现短暂毛刺(glitch),称为 静态冒险 。例如,当逻辑表达式 Y = A + ~A 应恒为1,但由于反相器延迟,中间可能出现瞬时0。

在状态机中,若输出直接来自组合逻辑,此类毛刺可能被下游电路误采样。解决方法包括:

- 添加冗余项 :使覆盖所有最小项跃迁;

- 使用格雷码编码 :限制状态跳变仅为一位;

- 输出寄存 :将输出锁存在时钟边沿。

示例:两输入多数表决电路 Y = AB + AC + BC

若A=B=C=1,之后A突变为0,路径AB先失效,AC和BC随后恢复,期间可能出现短暂低脉冲。

解决方案之一是加入共识项(consensus term):

assign Y = AB | AC | BC | (A & B & C); // Redundant term to suppress glitch

更优做法是将输出注册:

always @(posedge clk) Y_reg <= Y_comb;

这样即使组合逻辑有毛刺,也不会影响系统行为。

4.2.3 多变量逻辑优化工具在Verilog综合中的应用

现代EDA工具如Synopsys Design Compiler、Cadence Genus、Xilinx Vivado HLS均集成了高级逻辑优化引擎,支持:

- 代数因子分解(Algebraic Factoring)

- 共同子表达式消除(Common Subexpression Elimination)

- 状态编码自动选择

- 寄存器传输级(RTL)重构

例如,给定一段未优化代码:

assign out1 = (a & b) | (a & c);

assign out2 = (a & b) | (b & d);

综合工具会提取公共项 (a & b) 并复用,减少LUT使用量。

启用综合指令可进一步指导优化方向:

set_optimization_goal area

set_attribute [get_cells fsm_*] priority high

compile_ultra -no_boundary_optimization

这些策略在大规模SOC设计中尤为关键,直接影响PPA(Power, Performance, Area)指标。

5. 硬件描述语言建模与仿真验证

在现代数字系统设计中,硬件描述语言(HDL)不仅是电路功能的表达工具,更是连接架构构思、逻辑综合、物理实现与验证闭环的核心媒介。随着同步时序逻辑电路复杂度的不断提升,如何通过Verilog或VHDL精确建模其行为,并借助仿真与形式化手段确保设计正确性,已成为工程师必须掌握的关键能力。本章将深入探讨基于HDL的同步逻辑建模规范,重点解析两种主流语言在状态机实现中的差异与最佳实践,进而构建完整的验证流程体系——从测试平台搭建到覆盖率驱动验证,再到静态时序分析与违例修复。整个过程不仅强调语法层面的准确性,更注重语义一致性、可综合性以及工程可维护性的统一。

5.1 Verilog HDL中的同步逻辑建模规范

Verilog作为工业界最广泛使用的硬件描述语言之一,在同步时序电路建模方面具备高度灵活性和强大表达能力。然而,也正是这种灵活性带来了诸多潜在陷阱,尤其是在阻塞赋值与非阻塞赋值的选择、敏感列表完整性以及状态编码风格等方面。因此,建立一套标准化的建模规范对于提升代码质量、增强可读性和保障综合结果的确定性至关重要。

5.1.1 使用always @(posedge clk)块描述时序行为的标准范式

在Verilog中,所有与时钟边沿相关的状态更新都应封装在一个以 always @(posedge clk) 为触发条件的过程块中。这是同步设计的基本语法体现,也是EDA工具识别时序逻辑的关键依据。该结构确保了所有寄存器型变量的状态变化仅发生在时钟上升沿,符合同步系统的定义边界。

module sync_counter (

input clk,

input rst_n,

output reg [3:0] count

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

count <= 4'b0;

else

count <= count + 1'b1;

end

endmodule

逻辑逐行分析:

always @(posedge clk or negedge rst_n):此敏感列表包含时钟上升沿和复位信号下降沿,用于支持异步复位。这是常见的同步模块设计模式。if (!rst_n):检测低电平有效的异步复位信号。一旦有效,立即清零计数器。count <= 4'b0;:使用非阻塞赋值将count置零。即使多个赋值操作共存于同一块中,也能保证执行顺序不会影响最终结果。else count <= count + 1'b1;:在正常工作状态下进行递增操作,同样采用非阻塞赋值。

| 参数说明 | 含义 |

|---|---|

clk |

主系统时钟,驱动状态更新 |

rst_n |

异步复位信号,低电平有效 |

count |

4位寄存器输出,表示当前计数值 |

⚠️ 注意:虽然上述写法常见,但在高可靠性设计中推荐使用“同步复位”或“异步复位同步释放”结构,避免复位撤销时产生亚稳态。

此外,现代设计倾向于分离复位类型,如下所示为纯同步复位版本:

always @(posedge clk) begin

if (!rst_n)

count <= 4'b0;

else

count <= count + 1;

end

这种方式简化了时序路径分析,有利于静态时序验证(STA),但需注意上电初始化依赖外部电路保障。

流程图:同步逻辑建模决策路径

graph TD

A[开始设计同步逻辑] --> B{是否需要异步复位?}

B -- 是 --> C[使用 always @(posedge clk or negedge rst_n)]

B -- 否 --> D[使用 always @(posedge clk)]

C --> E[判断复位有效性]

D --> F[直接进入主逻辑]

E --> G[复位处理: 初始化状态]

F --> H[常规状态转移]

G --> I[非阻塞赋值更新寄存器]

H --> I

I --> J[结束过程块]

该流程图清晰地展示了从设计意图到具体语法选择之间的决策链条,帮助工程师规避因误用敏感列表而导致的行为偏差。

5.1.2 非阻塞赋值(<=)在状态更新中的必要性解释

在同步逻辑建模中,必须始终使用 非阻塞赋值 (Non-blocking Assignment, <= )来更新寄存器变量。这是因为非阻塞赋值模拟的是寄存器并行采样的物理特性——所有新值在时钟边沿后“同时”生效,而非按照代码书写顺序依次执行。

考虑以下错误示例:

always @(posedge clk) begin

a = b;

b = a;

end

若 a 和 b 初始均为0,下一个周期仍为0;但如果 b=1 ,则由于阻塞赋值的顺序执行特性, a 先被赋为1,随后 b 也被赋为1,导致数据交换意外发生,违背了同步寄存器独立更新的原则。

正确做法是:

always @(posedge clk) begin

a <= b;

b <= a;

end

此时, a 和 b 的更新基于 当前时刻的旧值 ,即实现了一个真正的双寄存器互换,符合预期行为。

| 赋值方式 | 执行机制 | 适用场景 | 示例 |

|---|---|---|---|

阻塞赋值 ( = ) |

立即执行,顺序更新 | 组合逻辑、局部变量计算 | temp = a & b; |

非阻塞赋值 ( <= ) |

延迟更新,统一在边沿后生效 | 时序逻辑、状态寄存器 | q <= d; |

进一步来看,在有限状态机中混合使用两种赋值可能导致灾难性后果。例如:

always @(posedge clk) begin

current_state = next_state; // 错误!应使用 <=

out = (current_state == S1) ? 1'b1 : 1'b0;

end

此处 current_state 若用阻塞赋值,则 out 会立即反映 next_state 的新值,破坏Moore机输出延迟一拍的特性。

因此,通用规则总结如下:

1. 所有在 posedge clk 块中的寄存器更新一律使用 <=

2. 只有在组合逻辑块(如 always @(*) )中才允许使用 = 进行中间信号计算

3. 避免在同一块中混用两者处理相关信号

5.1.3 参数化状态机编码风格与可重用模块设计

为了提升设计的可移植性和可配置性,应在Verilog中采用参数化状态编码方式。传统的宏定义方法虽可行,但缺乏类型安全和工具支持。推荐结合 typedef (SystemVerilog扩展)或纯 parameter 声明实现清晰的状态管理。

module fsm_example #(

parameter WIDTH = 3,

parameter S_IDLE = 3'd0,

parameter S_RUN = 3'd1,

parameter S_DONE = 3'd2

)(

input clk,

input rst_n,

input start,

output reg done

);

reg [WIDTH-1:0] state, next_state;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= S_IDLE;

end else begin

state <= next_state;

end

end

always @(*) begin

case(state)

S_IDLE: next_state = start ? S_RUN : S_IDLE;

S_RUN: next_state = (some_condition) ? S_DONE : S_RUN;

S_DONE: next_state = S_IDLE;

default: next_state = S_IDLE;

endcase

end

always @(posedge clk) begin

case(state)

S_RUN: done <= some_condition;

S_DONE: done <= 1'b1;

default: done <= 1'b0;

endcase

end

endmodule

参数说明:

- WIDTH :状态编码宽度,决定状态总数上限

- S_IDLE , S_RUN , S_DONE :预定义状态常量,便于修改编码方式(如改为独热码)

- state/next_state :采用分离式设计,提高可读性和综合效率

该设计具有良好的可重用性,只需更改参数即可适配不同项目需求。例如,若切换为独热码(One-hot),可重新定义:

parameter S_IDLE = 3'b001;

parameter S_RUN = 3'b010;

parameter S_DONE = 3'b100;

无需改动状态转移逻辑,极大提升了模块适应性。

表格:不同状态编码方式对比

| 编码方式 | 优点 | 缺点 | 典型应用场景 |

|---|---|---|---|

| 二进制编码 | 节省触发器资源 | 状态跳变多位,易引发毛刺 | 中小规模FSM |

| 独热码(One-hot) | 单比特翻转,速度快,便于调试 | 消耗更多FF,面积大 | 高速FPGA设计 |

| 格雷码 | 相邻状态仅一位变化,降低功耗 | 设计复杂,不适用于任意跳转 | 计数器类FSM |

| 自定义编码 | 可针对关键路径优化 | 需手动维护,易出错 | 特定性能要求场景 |

通过参数化设计,可在顶层设计中灵活指定编码策略,配合综合指令控制实际映射方式,实现性能与资源的最佳平衡。

5.2 VHDL语言的状态机实现方式

相较于Verilog,VHDL以其强类型系统和结构化语法著称,特别适合大型复杂系统的建模。在同步逻辑实现中,VHDL通过 process 语句明确区分时序与组合逻辑,提供了更高的安全性与可验证性。

5.2.1 process语句与clocked_process的结构组织

在VHDL中,所有时序行为均置于 process(clk) 中,并通过 if rising_edge(clk) 判断时钟边沿。标准模板如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity counter_vhdl is

Port (

clk : in STD_LOGIC;

rst_n : in STD_LOGIC;

count : out STD_LOGIC_VECTOR(3 downto 0)

);

end counter_vhdl;

architecture Behavioral of counter_vhdl is

signal cnt_reg : unsigned(3 downto 0);

begin

count <= std_logic_vector(cnt_reg);

sync_proc : process(clk, rst_n)

begin

if rst_n = '0' then

cnt_reg <= (others => '0');

elsif rising_edge(clk) then

cnt_reg <= cnt_reg + 1;

end if;

end process;

end Behavioral;

代码逻辑分析:

process(clk, rst_n):敏感列表显式列出所有输入信号,避免latch推断。rising_edge(clk):标准函数调用,比clk'event and clk='1'更安全。unsigned类型支持直接加法运算,无需手动扩展位宽。- 输出通过类型转换函数

std_logic_vector()对外暴露。

该结构符合IEEE推荐的同步建模范式,易于被综合工具识别为D触发器链。

5.2.2 枚举类型定义状态与综合工具识别能力

VHDL允许使用枚举类型定义状态,极大增强了代码可读性:

type state_type is (IDLE, RUN, DONE);

signal current_state, next_state : state_type;

综合工具(如Xilinx Vivado、Intel Quartus)能够自动将这些符号映射为二进制或用户指定的编码方式。更重要的是,VHDL的强类型检查可在编译阶段捕获非法状态赋值,防止运行时错误。

combinational : process(current_state, start)

begin

case current_state is

when IDLE =>

if start = '1' then

next_state <= RUN;

else

next_state <= IDLE;

end if;

when RUN =>

if finished = '1' then

next_state <= DONE;

else

next_state <= RUN;

end if;

when DONE =>

next_state <= IDLE;

when others =>

next_state <= IDLE;

end case;

end process;

这里的 when others 分支是必要的防御性编程,防止未定义状态导致不确定行为。

5.2.3 属性说明(attribute)对状态编码的强制指定

VHDL支持通过属性(attribute)精确控制状态编码方式。例如,强制使用独热码:

attribute ENUM_ENCODING : string;

attribute ENUM_ENCODING of state_type : type is "100 010 001";

该属性指示综合器将 IDLE=100 , RUN=010 , DONE=001 ,从而实现独热编码。这在高性能设计中尤为关键,能显著减少组合逻辑层级,提升最大工作频率。

5.3 功能仿真与测试平台构建

5.3.1 编写激励生成模块(testbench)的关键要素

一个完整的testbench应包括:

- 时钟与复位信号生成

- 输入激励序列

- 波形监控与断言检查

- 覆盖率收集机制

// Testbench for sync_counter

module tb_sync_counter;

reg clk, rst_n;

wire [3:0] count;

// 实例化被测单元

sync_counter uut (

.clk(clk),

.rst_n(rst_n),

.count(count)

);

// 生成时钟

always #5 clk = ~clk;

initial begin

clk = 0;

rst_n = 0;

#10 rst_n = 1;

#100 $display("Count reached: %d", count);

#200 $finish;

end

// 断言检查

initial begin

forever @(posedge clk) begin

assert property (count >= 0 && count <= 15)

else $error("Counter out of range!");

end

end

endmodule

5.3.2 波形观察与断言检查在调试中的协同使用

结合Waveform Viewer(如ModelSim、VCS)与SystemVerilog Assertions(SVA),可实现高效调试。

5.3.3 覆盖率驱动验证(coverage-driven verification)流程导入

利用功能覆盖率( covergroup )、代码覆盖率(line/toggle/branch)指导测试用例生成,确保充分验证所有状态迁移路径。

5.4 形式化验证与时序分析

5.4.1 静态时序分析(STA)报告解读与关键路径定位

STA工具(如PrimeTime)输出建立/保持时间违例,需结合布局布线信息定位瓶颈。

5.4.2 使用EDA工具进行建立/保持时间违例修复

可通过插入缓冲器、调整逻辑层级、优化寄存器配对等方式修复时序问题。

5.4.3 综合后网表与布局布线后时序反标的重要性

反标SDF文件至仿真环境,实现门级时序仿真,验证真实延迟下的功能正确性。

6. 典型同步电路设计实例与工程实战

6.1 同步计数器系列设计

同步计数器是数字系统中最基础且广泛应用的时序模块之一,其所有触发器共享同一个时钟信号,在每个时钟上升沿同时更新状态。相比异步计数器,同步结构避免了级联延迟累积问题,显著提升最大工作频率。

6.1.1 四位二进制加法计数器的Verilog实现与级联扩展

以下是一个基于D触发器构建的四位同步二进制加法计数器的Verilog代码示例:

module binary_counter_4bit (

input clk,

input reset,

input enable,

output reg [3:0] count

);

always @(posedge clk) begin

if (reset)

count <= 4'b0000;

else if (enable)

count <= count + 1;

end

endmodule

参数说明:

- clk :主时钟输入(通常为50MHz或更高)

- reset :高电平有效异步复位,强制清零

- enable :使能信号,控制是否递增

- count[3:0] :当前计数值输出

该计数器可在FPGA上综合后实现最大理论频率达200MHz以上(取决于工艺和布局布线)。若需扩展为8位或更高位宽,可通过级联方式连接多个模块,并将低位计数器的溢出信号(如 &count[3:0] )作为高位模块的使能条件。

6.1.2 可逆计数器的方向控制逻辑与同步加载功能集成

增强型同步计数器支持双向计数及预置值加载,适用于电机控制、ADC接口等场景。以下是带方向选择和同步加载功能的8位可逆计数器实现片段:

module up_down_counter_load (

input clk,

input reset,

input load,

input direction, // 1: up, 0: down

input enable,

input [7:0] data_in,

output reg [7:0] count

);

always @(posedge clk) begin

if (reset)

count <= 8'd0;

else if (load)

count <= data_in; // 同步加载

else if (enable) begin

if (direction)

count <= count + 1;

else

count <= count - 1;

end

end

endmodule

此设计中, load 信号优先级高于计数操作,确保在任意时刻都能准确设置初始状态。

6.1.3 BCD码十进制计数器的进位处理技巧

BCD计数器每到9后自动归零并产生进位脉冲,常用于数码管驱动。关键在于检测 count == 4'd9 并强制下一时钟周期清零:

always @(posedge clk) begin

if (reset)

count <= 4'd0;

else if (enable) begin

if (count == 4'd9)

count <= 4'd0;

else

count <= count + 1;

end

end

assign carry = (count == 4'd9) && enable;

这种“模10”行为通过组合逻辑判断实现,无需额外状态机,简洁高效。

6.2 移位寄存器及其变体应用

移位寄存器是数据序列化/反序列化的关键组件,广泛用于通信协议、LED控制等领域。

6.2.1 串入并出(SIPO)移位寄存器用于LED流水灯控制

一个典型的SIPO结构如下:

module sipo_register (

input clk,

input reset,

input si,

output reg [7:0] po

);

always @(posedge clk or posedge reset) begin

if (reset)

po <= 8'b0000_0001; // 初始点亮第一个LED

else begin

po <= {po[6:0], si}; // 左移一位,新数据从最低位进入

end

end

endmodule

配合外部移位时钟,可实现LED逐一点亮效果。实际项目中常使用专用IP核或SPI控制器替代手动编码。

6.2.2 并入串出(PISO)结构在数据压缩接口中的运用

PISO允许并行加载数据后逐位输出,适用于传感器数据打包发送:

module piso_register (

input clk,

input load,

input [7:0] pi,

output reg so

);

reg [7:0] shift_reg;

always @(posedge clk) begin

if (load)

shift_reg <= pi;

else

shift_reg <= {shift_reg[6:0], 1'b0};

so <= shift_reg[7];

end

endmodule

每次移位后最高位输出至 so ,共需8个周期完成传输。

6.2.3 环形计数器与约翰逊计数器的自循环特性分析

| 类型 | 状态序列(4位) | 周期 | 特点 |

|---|---|---|---|

| 环形计数器 | 1000 → 0100 → 0010 → 0001 → 1000 | 4 | 单‘1’循环,简单易控 |

| 约翰逊计数器 | 0000 → 1000 → 1100 → 1110 → 1111 → 0111 → 0011 → 0001 → 0000 | 8 | 格雷码近似,无毛刺跳变 |

两者均可用移位寄存器加反馈构成,适合低功耗定时器设计。

stateDiagram-v2

[*] --> S0

S0 --> S1 : clk↑

S1 --> S2 : clk↑

S2 --> S3 : clk↑

S3 --> S0 : clk↑

note right of S3

环形计数器状态转移图

end note

6.3 复杂状态机项目实战

6.3.1 序列检测器(如“1101”模式识别)的状态图构建

采用Mealy型FSM检测串行输入流中出现“1101”序列。定义四个状态:

- S0:初始/等待‘1’

- S1:已接收‘1’

- S2:已接收‘11’

- S3:已接收‘110’

状态转移表如下:

| 当前状态 | 输入 | 下一状态 | 输出 |

|---|---|---|---|

| S0 | 0 | S0 | 0 |

| S0 | 1 | S1 | 0 |

| S1 | 0 | S0 | 0 |

| S1 | 1 | S2 | 0 |

| S2 | 0 | S3 | 0 |

| S2 | 1 | S2 | 0 |

| S3 | 0 | S0 | 0 |

| S3 | 1 | S0 | 1 |

输出仅在S3状态下输入‘1’时有效。

6.3.2 交通灯控制系统中的多相位切换逻辑实现

设计东西-南北双路交叉口控制,每周期包含绿→黄→红三个阶段。使用Moore机建模:

typedef enum logic [1:0] {GREEN_EW, YELLOW_EW, GREEN_NS, YELLOW_NS} state_t;

state_t current_state, next_state;

always @(posedge clk) begin

if (reset) current_state <= GREEN_EW;

else current_state <= next_state;

end

always @(*) begin

case (current_state)

GREEN_EW: next_state = (timer_done) ? YELLOW_EW : GREEN_EW;

YELLOW_EW: next_state = (timer_done) ? GREEN_NS : YELLOW_EW;

GREEN_NS: next_state = (timer_done) ? YELLOW_NS : GREEN_NS;

YELLOW_NS: next_state = (timer_done) ? GREEN_EW : YELLOW_NS;

endcase

end

定时器由分频器驱动,确保各相位持续时间可控。

6.3.3 UART发送器状态机设计与时钟分频配合

UART发送需将并行字节转换为串行帧(起始位+8数据位+停止位),波特率依赖系统时钟分频。典型状态机包括:

- IDLE:等待发送请求

- START:输出低电平起始位

- DATAx:依次发送bit0~bit7

- STOP:输出高电平停止位

假设系统时钟50MHz,目标波特率115200,则分频系数 ≈ 270.8 → 取整271。

localparam CLK_DIV = 271;

reg [8:0] clk_count;

wire baud_tick = (clk_count == (CLK_DIV - 1));

always @(posedge clk) begin

if (baud_tick) begin

clk_count <= 0;

bit_tick <= 1;

end else begin

clk_count <= clk_count + 1;

bit_tick <= 0;

end

end

结合状态机实现精确时序控制。

6.4 教学实验项目指导与错误排查

6.4.1 常见设计误区:混淆阻塞与非阻塞赋值导致的竞争

在时序逻辑中误用阻塞赋值( = )会导致仿真与综合结果不一致:

❌ 错误写法:

always @(posedge clk) begin

a = b;

c = a; // 此处a尚未更新,c取旧值

end

✅ 正确写法:

always @(posedge clk) begin

a <= b;

c <= a; // 所有<=操作在块末统一更新

end

建议:所有时序逻辑一律使用非阻塞赋值。

6.4.2 未初始化状态变量引发的上电不确定行为

FPGA上电后寄存器初值不可预测。应在复位路径中显式初始化:

always @(posedge clk) begin

if (!rst_n) begin

state <= IDLE; // 必须指定默认状态

tx_data <= 8'd0;

end else ...

end

否则可能出现非法状态停滞。

6.4.3 28个精选实例源码解析:从基础到综合系统的演进路径

提供涵盖以下类型的完整工程案例:

1. 4位同步加法计数器

2. 可预置减法计数器

3. BCD计数器级联显示小时分钟

4. 8位SIPO流水灯

5. PISO读取ADC数据

6. 环形计数器驱动步进电机

7. 约翰逊计数器生成三相时钟

8. “1011”序列检测器(Mealy)

9. 安全密码锁状态机

10. 自动售货机投币逻辑

11. 电梯楼层控制器

12. 简易CPU指令译码器

13. SPI主设备发送模块

14. I2C起始/停止信号生成

15. PWM调光控制器

16. 频率计测量外部信号

17. 数码管动态扫描驱动

18. 温度报警阈值监测

19. 按键去抖动有限状态机

20. RS232回环测试装置

21. VGA行场同步发生器

22. PS/2键盘解码器

23. CRC校验生成器

24. FIFO缓冲区管理

25. 双端口RAM读写控制

26. 异步FIFO跨时钟域同步

27. SDRAM初始化序列控制器

28. 基于状态机的HTTP响应解析器(嵌入式Web服务器)

每个实例附带Testbench激励、波形截图、综合报告及时序约束文件(SDC),帮助开发者理解从建模到部署的全流程。

简介:同步时序逻辑电路是数字电子技术的核心内容,广泛应用于计数、数据存储和状态控制等场景。本压缩包包含28个由作者精心设计的同步时序逻辑电路实例,涵盖二进制计数器、环形计数器、移位寄存器等典型电路,提供完整的源文件与解析说明。通过这些实例,读者可深入理解触发器、时钟信号、组合逻辑与状态寄存器的协同工作机制,掌握从状态分析、编码到逻辑实现与仿真的完整设计流程,适用于学习、教学及工程实践。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)