基于XILINX Vivado平台的GTX收发器的开发

参考资料:《ug476_7Series_Transceivers》此项目包含开发源码,各位同学要是有地方需要改进,敬请指出!

参考资料:《ug476_7Series_Transceivers》

此项目包含开发源码,各位同学要是有地方需要改进,敬请指出!

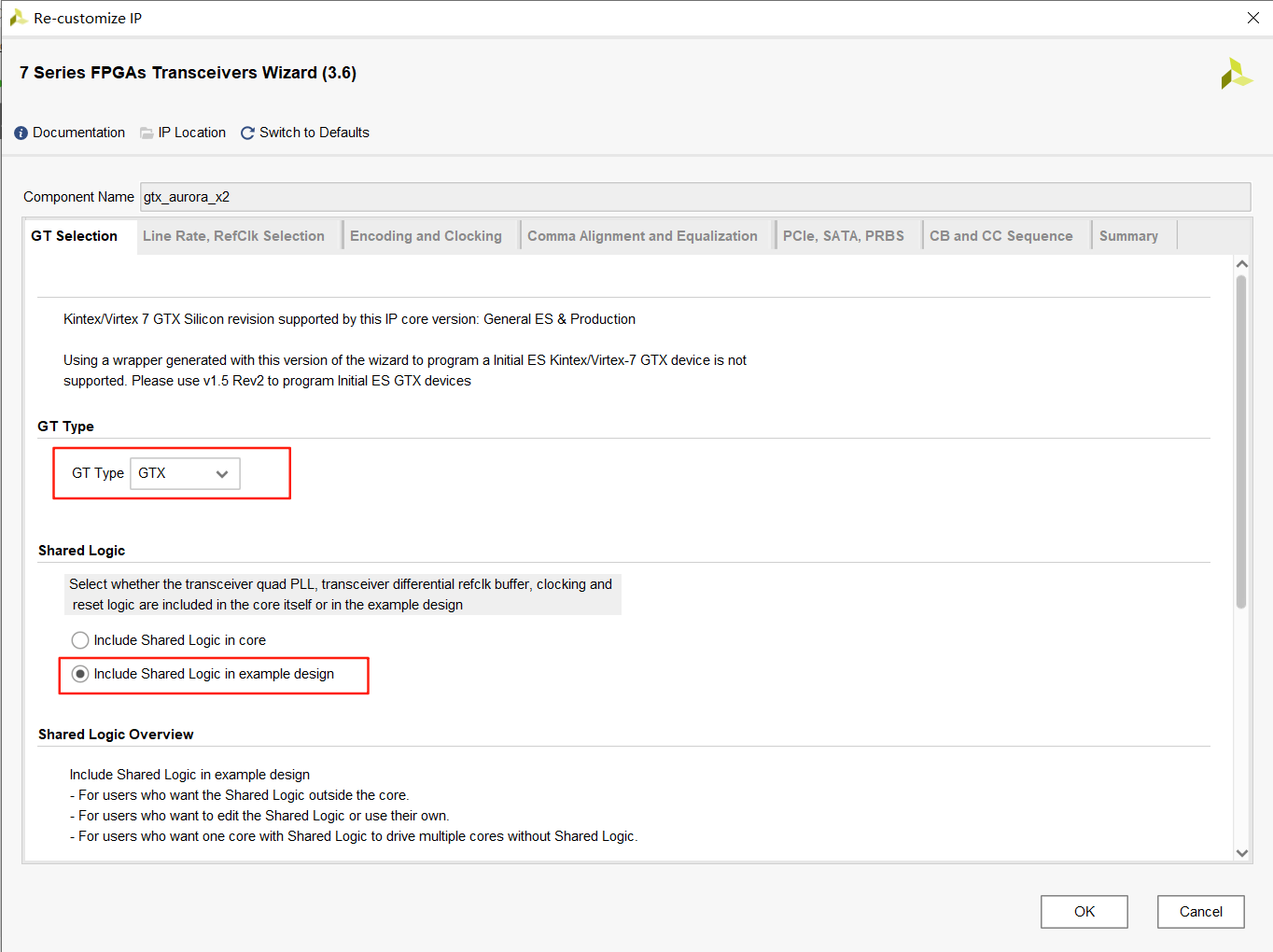

1. GTX IP核的创建

此选项根据你所用的FPGA型号确定GT类型,我所用的是7k325t系列,故GT类型为GTX

接下来,开始配置IP

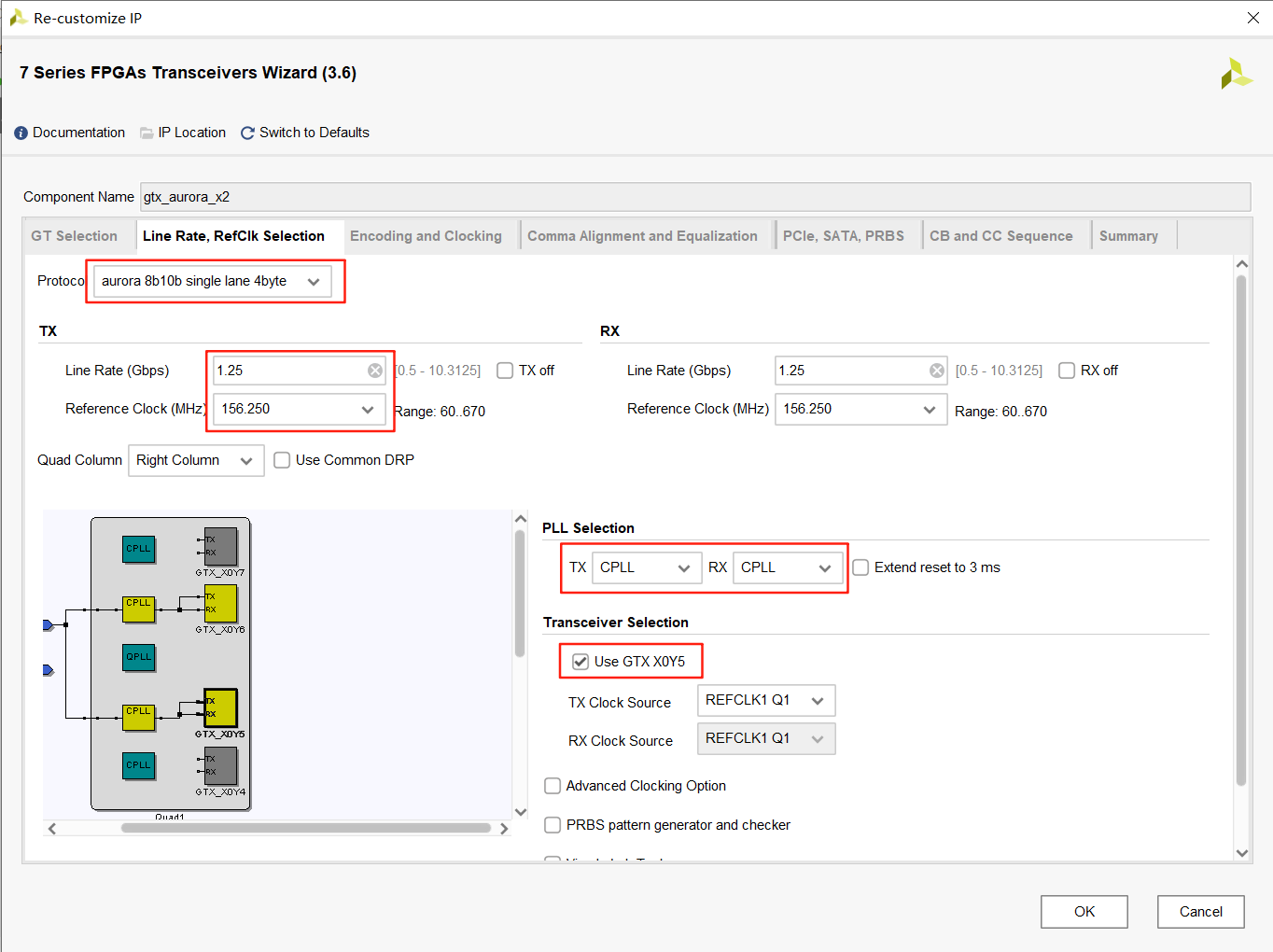

首先,这里的时钟频率是连接FPGA高速bank上的差分时钟,根据自己项目实际需求进行配置即可

再者,强调一下,因为我的项目中对应的是光纤收发,线速率根据实际光口的不同进行适配选择即可!

还有,估计有和我当时一样的初学者看本篇文章,所以我就本着我当时初学时复杂且全是问号?的心情补充一下。开始废话(高手跳过):我这里是两个高速收发器,亦就是两路光纤收发,怎么来的呢,当然是选的,怎么选的呢,好问题,用你的鼠标选中左侧灰色的收发器框图,然后点击选择我用小红框标记的选项“Use GTX X0Y6”,然后框图从灰色变成黄色了,这个时候神奇的事情就发生了,艾~突然就又增加了一个,聪明的你就以此类推了,哈哈哈哈,这个框图你得对照你项目中实际原理图看仔细,你用的高速收发器是在哪个FPGAbank上的哪个坐标就行,不过也没关系,就算这里你选错了,到时候你约束引脚约束对了就可以了,不影响的。

好了,接着选

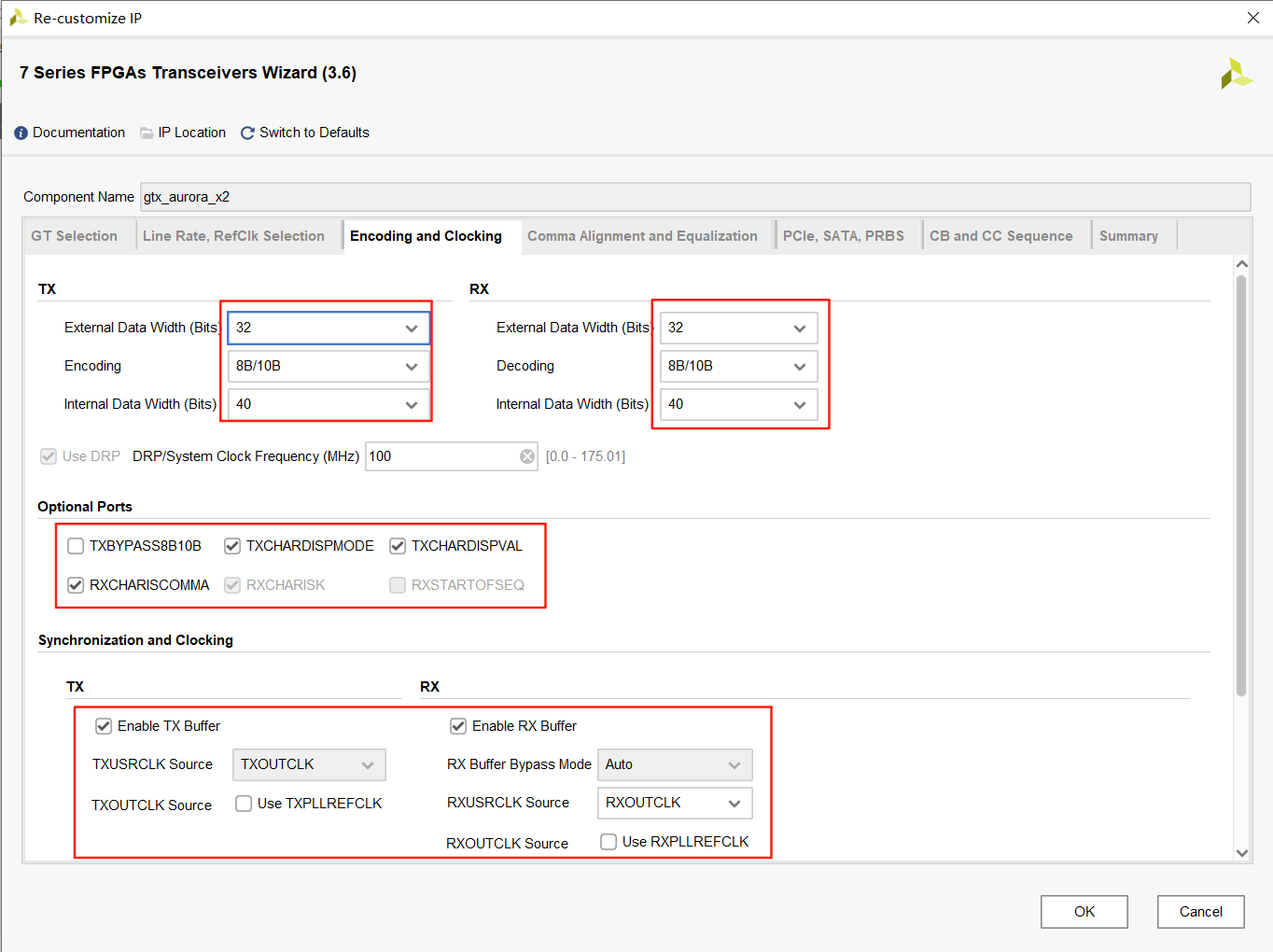

这里就开始配置收发器了,外部数据宽度,也就是咱们逻辑里面最终要用到的数据位宽,这里我用的是32位,根据你项目需求用就行了,就算其他位宽的,你用异步fifo转不就行了,这能难倒咱们逻辑工程师吗?开玩笑呢!好,编码一般8B/10B,内部数据位宽就得注意了,这个地方还与最终咱们使用的userclk有关,在ug476手册里面第100页有具体讲解(广子:上xianyu搜麻酱就烧饼,获取xilinx全系列文档手册),可以自己查查,我就简单赘述两句: TXUSRCLK Rate=Line Rate/Internal Datapath Width,如果这里你的内部位宽是20的时候,你最终的TXUSERCLK2=TXUSERCLK/2,具体细节深耕数据手册!

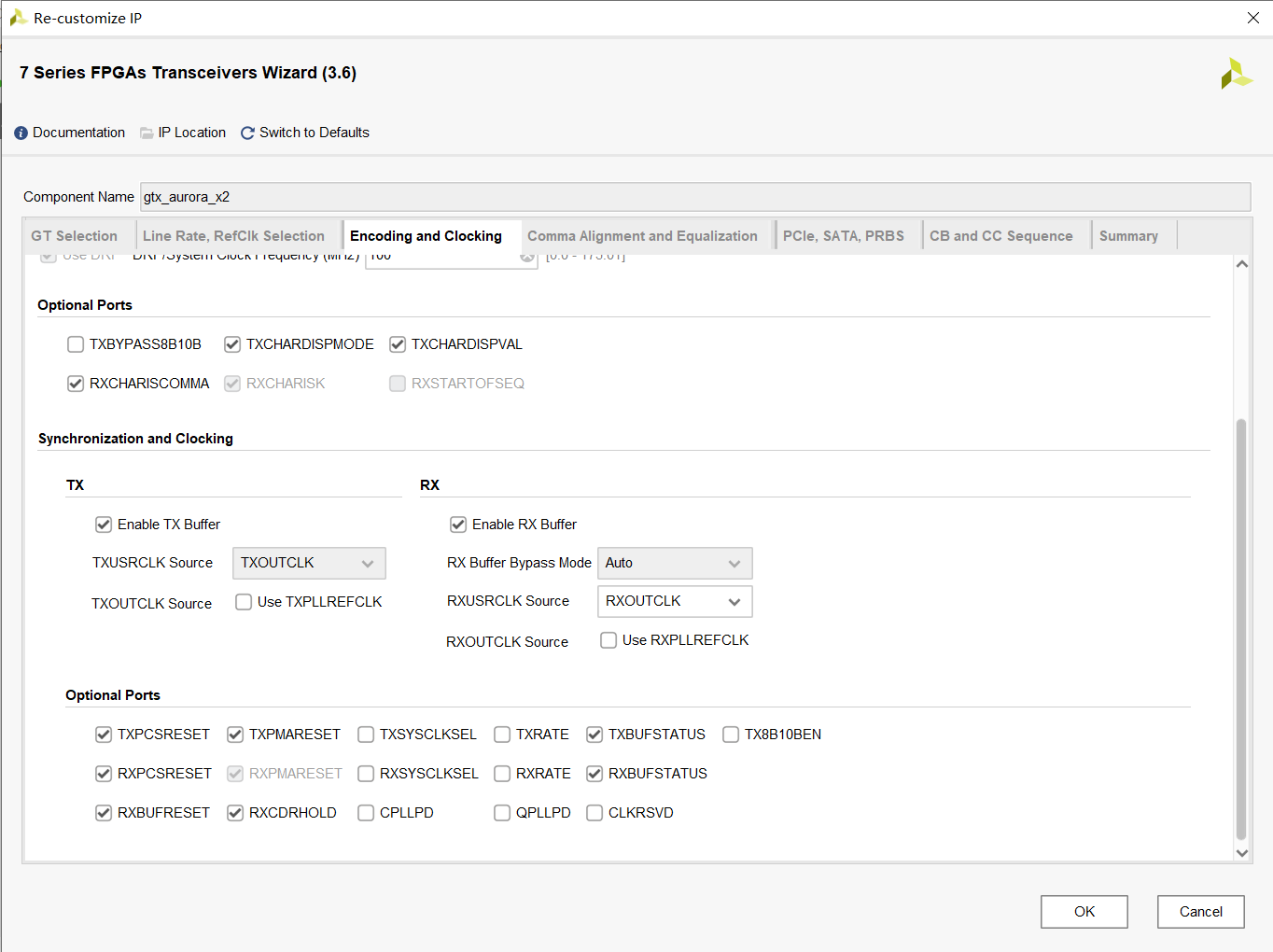

然后就是本页其他配置都是默认的,不用管(如果有特殊需求除外)

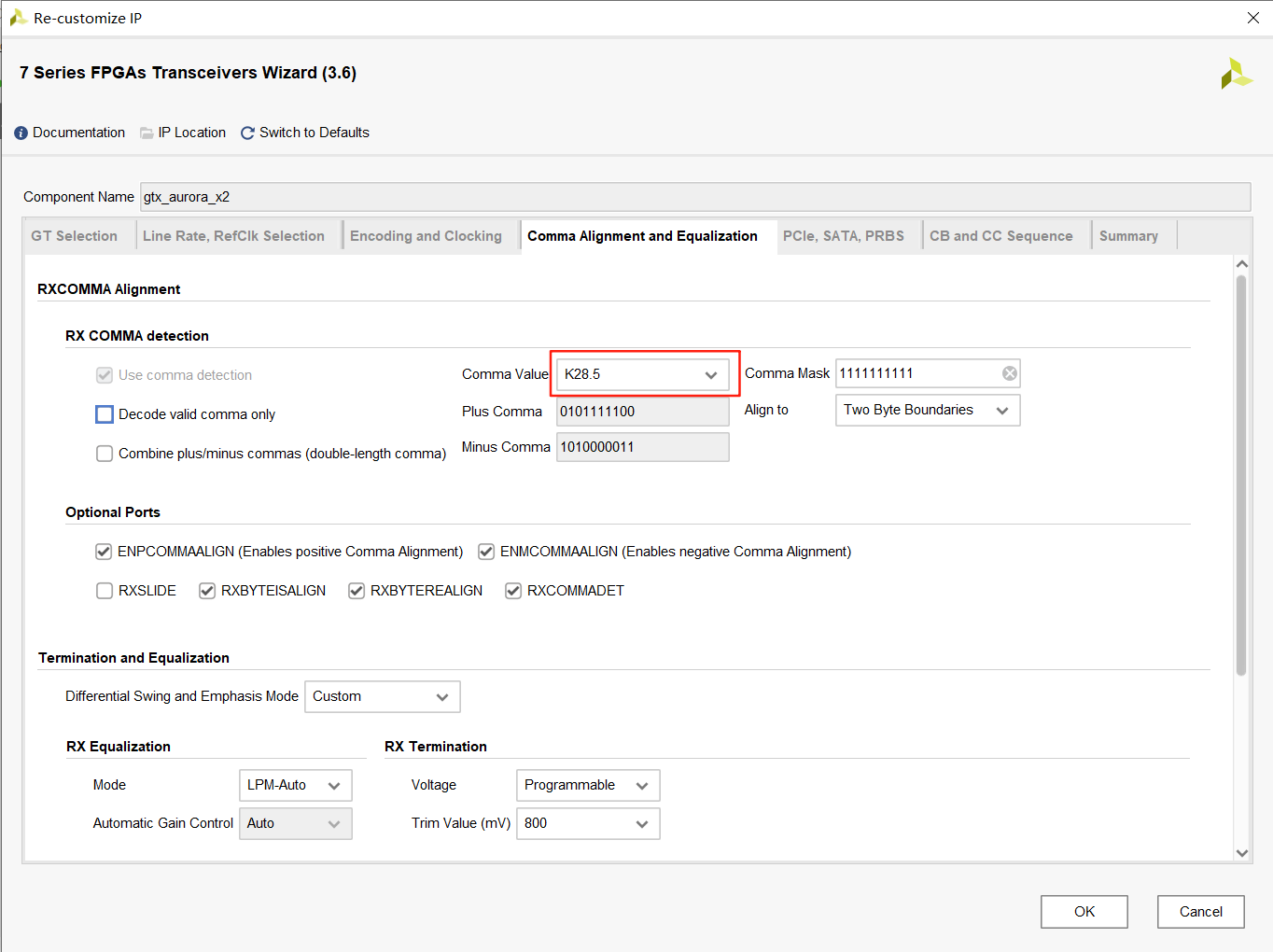

接着选,Comma Value我用的K28.5(BC码),具体看我源码中如何使用,其他配置默认!

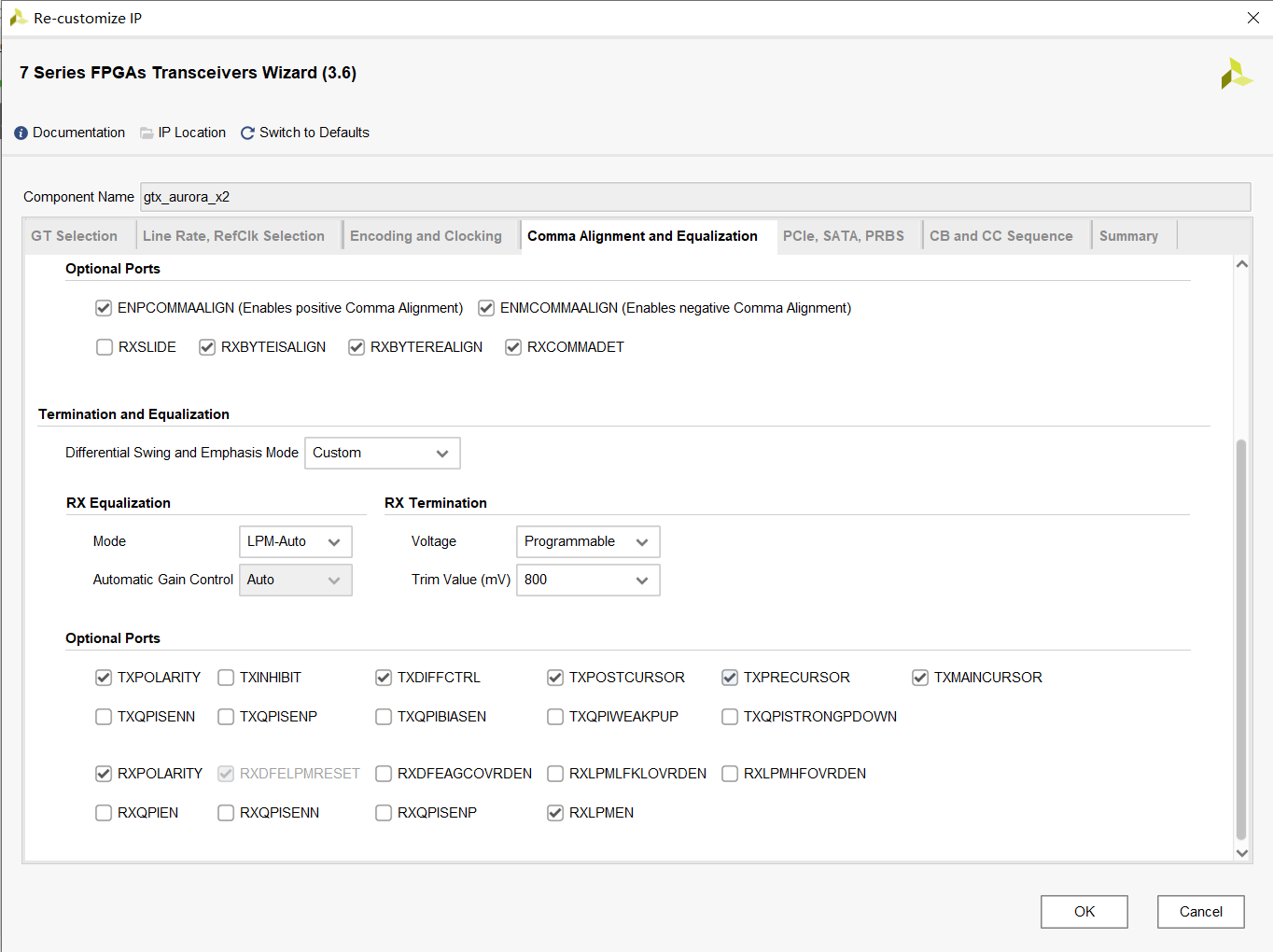

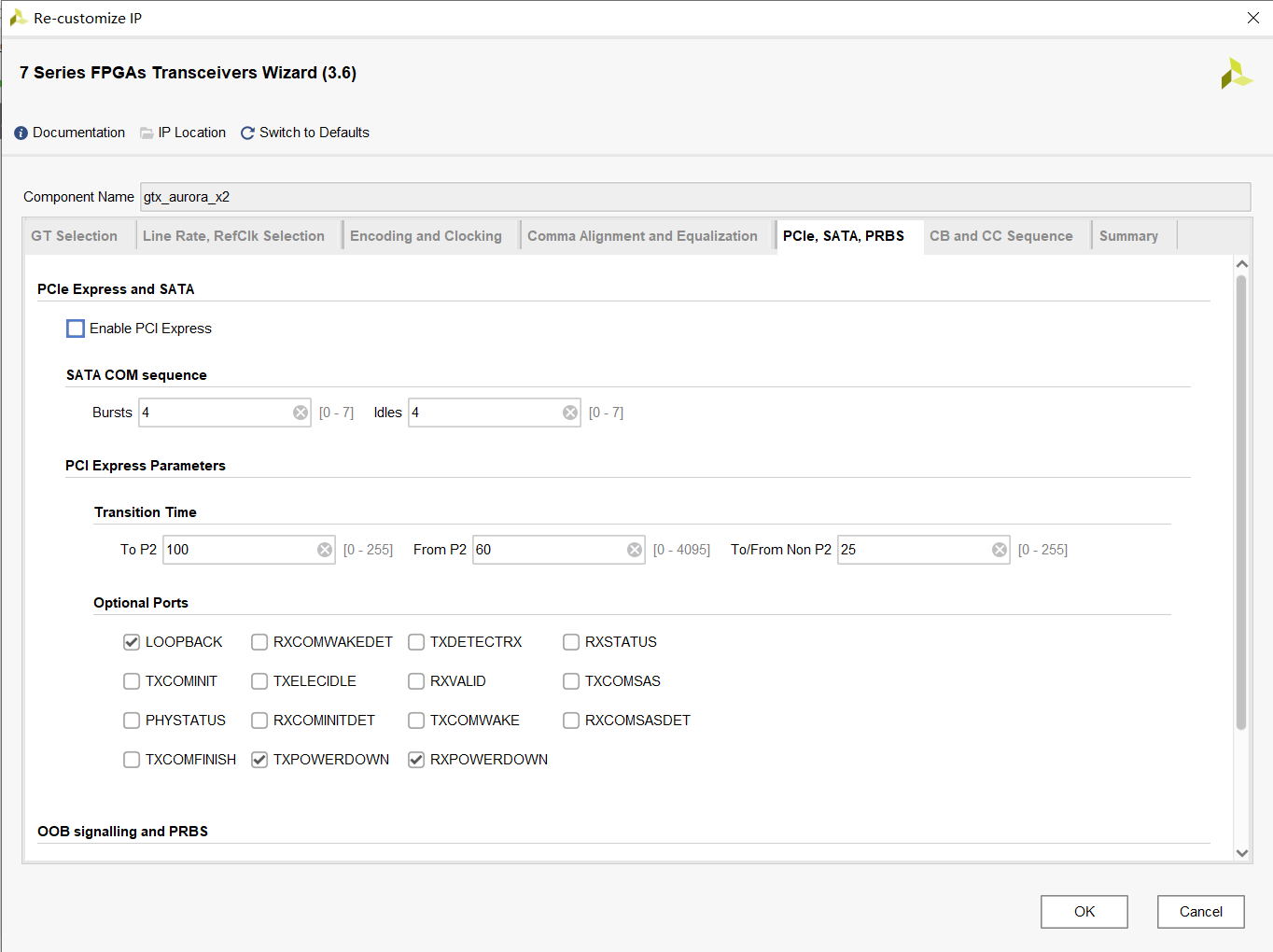

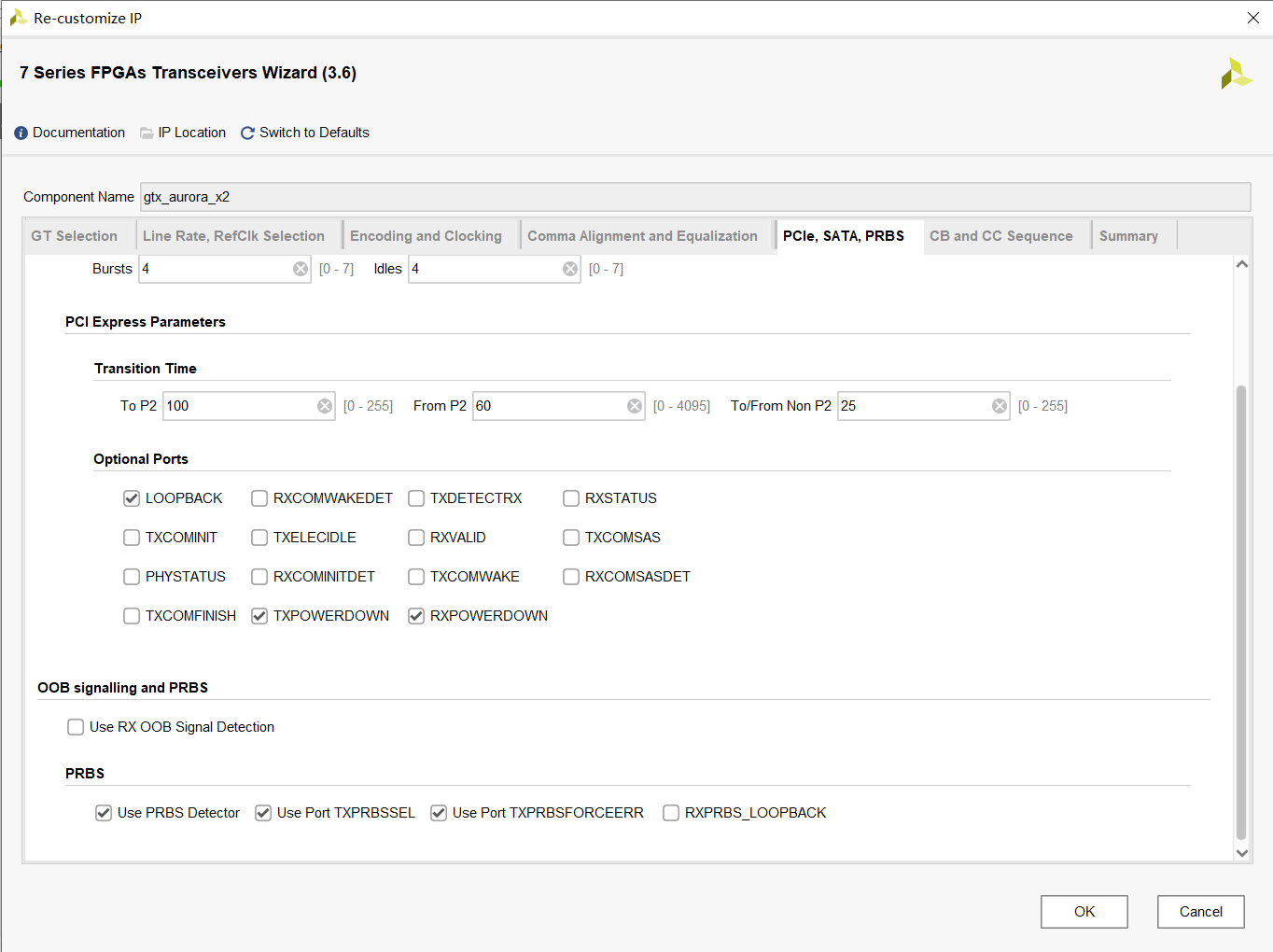

接着来,不用管,继续默认

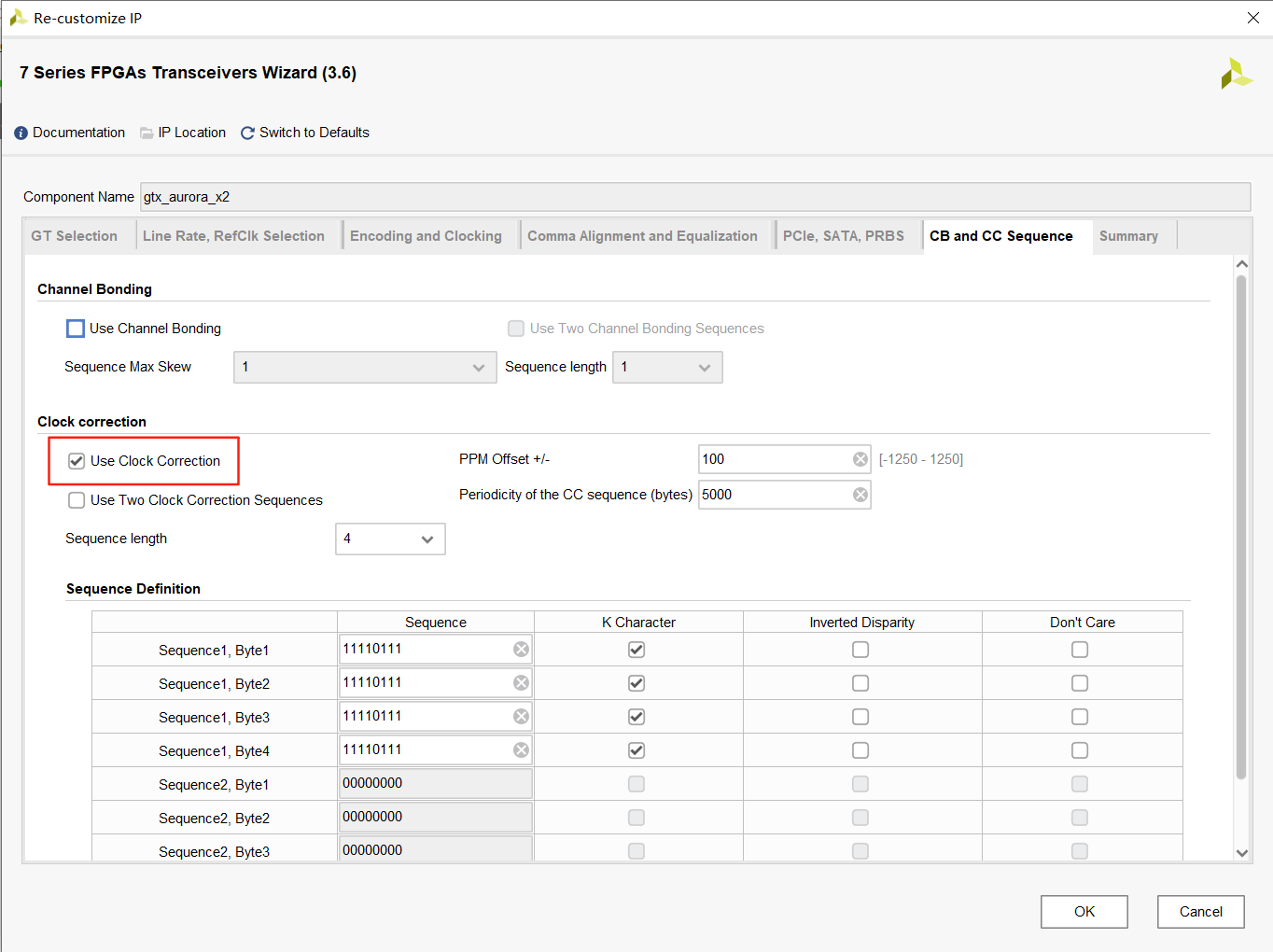

继续来,勾选USE CLOCK CORRECTION,其余默认

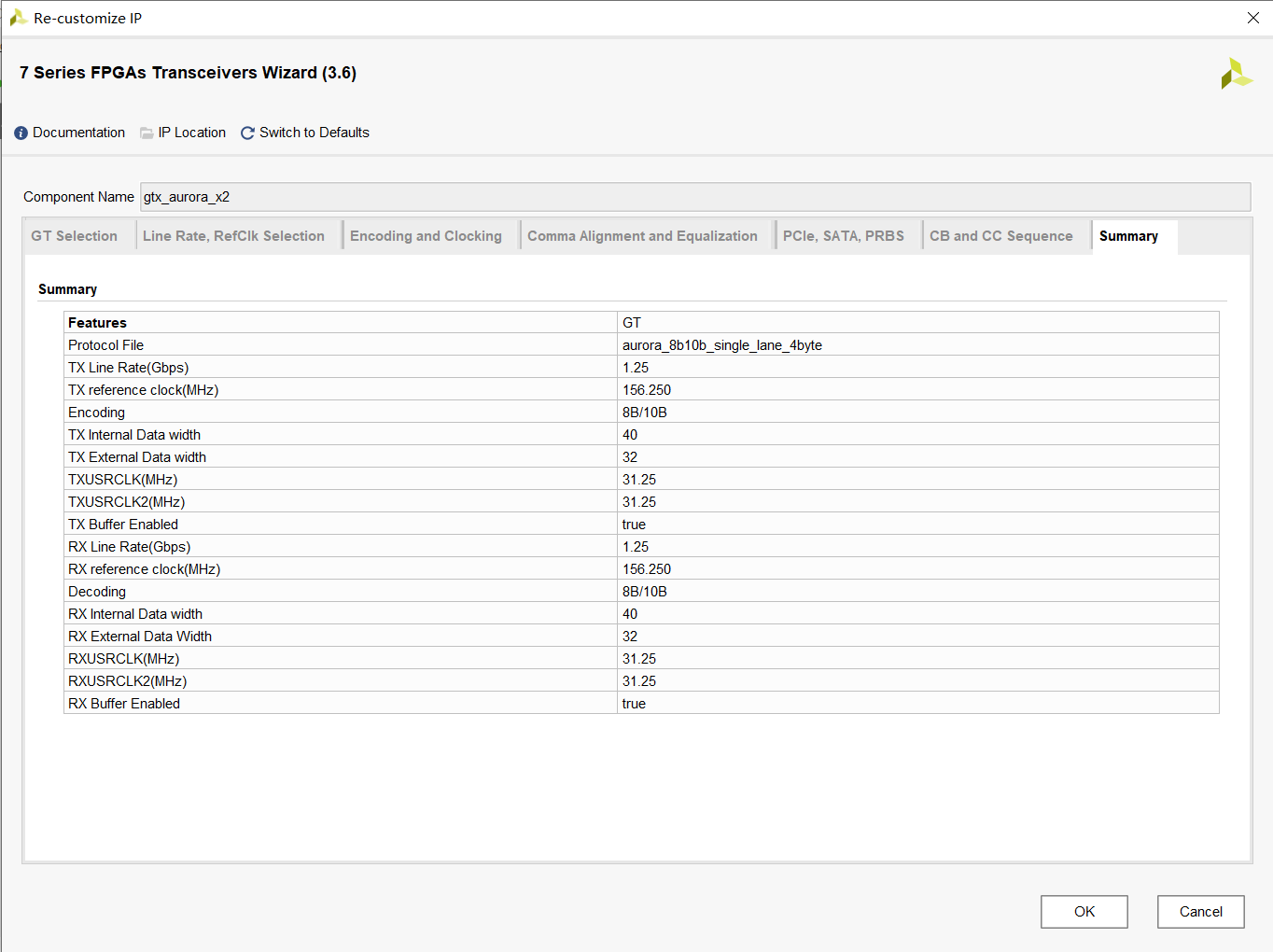

最后检查所配置结束的IP参数,强调:最后我们在逻辑里面发送用的时钟域是TXUSRCLK2,以此类推,接收用RXUSRCLK2!!!

2. 搭建工程且编码

好了,咱们开始爆改啊啊啊啊啊啊啊!

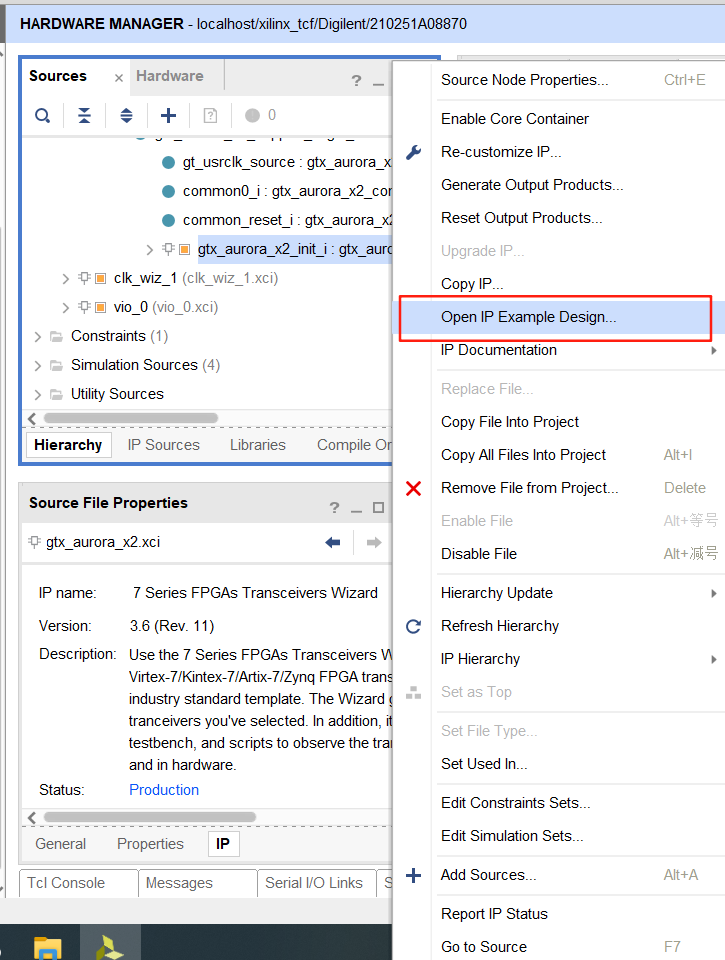

生成例程,完了只需修改例程顶层模块gtx_aurora_x2_exdes.v文件即可

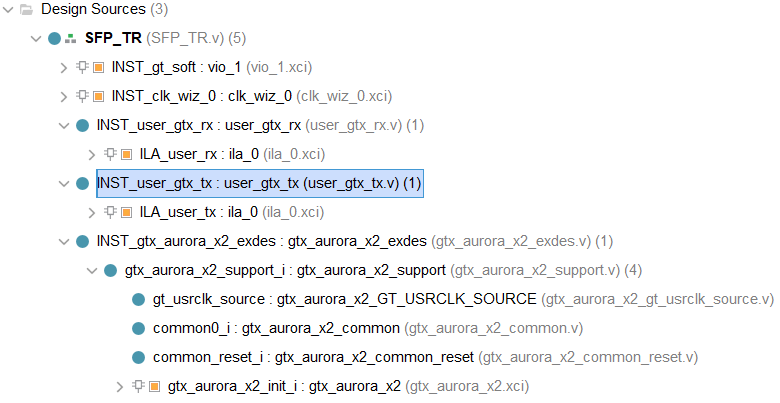

工程结构:

我在编码模块中用到了状态机,而在解码模块中没有用到,原则是:怎么简明怎么来

顶层:

描述:顶层当中的sys_on_sim在实际使用时换成sys_on即可!

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: FPGA NXH

//

// Create Date: 2025/06/09 10:56:46

// Design Name:

// Module Name: SFP_TR

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module SFP_TR(

input CLK_i,

input SFP_CLK_IN_P,

input SFP_CLK_IN_N,

input [1:0] SFP_2X_IN_P,

input [1:0] SFP_2X_IN_N,

output [1:0] SFP_2X_OUT_P,

output [1:0] SFP_2X_OUT_N,

output [3:0] state_led

);

//---------------clk and reset-----------------

wire sys_clk;

wire sys_rstn;

//---------------user rx-----------------------

wire user_rx0_clk;

wire [31:0] user_rx0_data;

wire [3:0] user_rx0_kdata;

wire user_rx0_link;

wire user_rx1_clk;

wire [31:0] user_rx1_data;

wire [3:0] user_rx1_kdata;

wire user_rx1_link;

wire [31:0] rX0_data;

wire rX0_data_vld;

wire [31:0] rX1_data;

wire rX1_data_vld;

//---------------user tx-----------------------

wire user_tx0_clk;

wire [31:0] tx0_data;

wire [3:0] tx0_kdata;

wire user_tx0_link;

wire user_tx1_clk;

wire [31:0] tx1_data;

wire [3:0] tx1_kdata;

wire user_tx1_link;

//---------------vio-------------------------------

wire sys_on_sim;

wire soft_vld;

wire soft_rst_tx_vio;

wire soft_rst_rx_vio;

wire [2:0] gt_loopback_vio;

wire soft_rst_tx_vio_r;

wire soft_rst_rx_vio_r;

wire [2:0] gt_loopback_vio_r;

vio_1 INST_gt_soft (

.clk (sys_clk ), // input wire clk

.probe_out0 (soft_vld ), // output wire [0 : 0] probe_out0

.probe_out1 (soft_rst_tx_vio_r ), // output wire [0 : 0] probe_out1

.probe_out2 (soft_rst_rx_vio_r ), // output wire [0 : 0] probe_out2

.probe_out3 (gt_loopback_vio_r ), // output wire [2 : 0] probe_out3

.probe_out4 (sys_on_sim ) // output wire [0 : 0] probe_out4

);

assign soft_rst_tx_vio = soft_vld ? soft_rst_tx_vio_r : 'h0;

assign soft_rst_rx_vio = soft_vld ? soft_rst_rx_vio_r : 'h0;

assign gt_loopback_vio = soft_vld ? gt_loopback_vio_r : 'h0;

//-------------------sys_on-----------------------------

wire sys_on;

reg [4:0] user_tx0_link_r='h0;

reg [4:0] user_tx1_link_r='h0;

always @ (posedge user_tx0_clk) user_tx0_link_r <= {user_tx0_link_r[3:0], user_tx0_link};

always @ (posedge user_tx1_clk) user_tx1_link_r <= {user_tx1_link_r[3:0], user_tx1_link};

assign sys_on = (user_tx0_link_r[4] && user_tx1_link_r[4]) ? 'h1 : 'h0;

//-------------------CLK--------------------------------

clk_wiz_0 INST_clk_wiz_0(

// Clock out ports

.clk_out1 (sys_clk), // output clk_out1

// Status and control signals

.reset (1'b0), // input reset

.locked (sys_rstn), // output locked

// Clock in ports

.clk_in1 (CLK_i) // input clk_in1

);

//-----------------USER RX------------------------------

user_gtx_rx #

(

.DATA_WIDTH (32),

.KCHAR_WIDTH (4)

)

INST_user_gtx_rx (

.clk (sys_clk),

.rstn (sys_rstn),

.rx0_clk (user_rx0_clk),

.rx0_link (user_rx0_link),

.rx0_data (user_rx0_data),

.rx0_kdata (user_rx0_kdata),

.rx1_clk (user_rx1_clk),

.rx1_link (user_rx1_link),

.rx1_data (user_rx1_data),

.rx1_kdata (user_rx1_kdata),

.user_rx0_data (rx0_data),

.user_rx0_data_vld (rx0_data_vld),

.user_rx1_data (rx1_data),

.user_rx1_data_vld (rx1_data_vld)

);

//-----------------USER TX------------------------------

user_gtx_tx #

(

.DATA_WIDTH (32),

.KCHAR_WIDTH (4)

)

INST_user_gtx_tx(

.clk (sys_clk),

.rstn (sys_rstn),

.sys_on (sys_on_sim),

.tx0_clk (user_tx0_clk),

.tx0_link (user_tx0_link),

.tx0_data (tx0_data),

.tx0_kdata (tx0_kdata),

.tx1_clk (user_tx1_clk),

.tx1_link (user_tx1_link),

.tx1_data (tx1_data),

.tx1_kdata (tx1_kdata)

);

//-----------------GTX-----------------------------------

gtx_aurora_x2_exdes INST_gtx_aurora_x2_exdes(

.Q1_CLK1_GTREFCLK_PAD_N_IN (SFP_CLK_IN_N),

.Q1_CLK1_GTREFCLK_PAD_P_IN (SFP_CLK_IN_P),

.DRP_CLK_IN (sys_clk),

.RXN_IN (SFP_2X_IN_N),

.RXP_IN (SFP_2X_IN_P),

.TXN_OUT (SFP_2X_OUT_N),

.TXP_OUT (SFP_2X_OUT_P),

//-------------user interface-------------------------

.soft_rst_tx (soft_rst_tx_vio),

.soft_rst_rx (soft_rst_rx_vio),

.gt_loopback (gt_loopback_vio_r),

.user_rx0_clk (user_rx0_clk),

.user_rx0_data (user_rx0_data),

.user_rx0_kdata (user_rx0_kdata),

.user_rx0_link (user_rx0_link),

.user_rx1_clk (user_rx1_clk),

.user_rx1_data (user_rx1_data),

.user_rx1_kdata (user_rx1_kdata),

.user_rx1_link (user_rx1_link),

.user_tx0_clk (user_tx0_clk),

.user_tx0_data (tx0_data),

.user_tx0_kdata (tx0_kdata),

.user_tx0_link (user_tx0_link),

.user_tx1_clk (user_tx1_clk),

.user_tx1_data (tx1_data),

.user_tx1_kdata (tx1_kdata),

.user_tx1_link (user_tx1_link)

);

//-----------------PORT-----------------------------------

assign state_led = {user_tx0_link, user_tx1_link, user_rx0_link, user_rx1_link};

//-----------------DEBUG-----------------------------------

endmodule

打包编码:

编码选用8b/10b,comma值用k28.5(BC码),有同学就好奇,k28.5为啥就是BC码,好吧,我当时也不懂艾,好在去取经了,现在就给你道来:0XBC=0B1011 1100,好,重点来了,0D28=0B11100,0D5=0B101,聪明的你已经发现了,BC=5和28相结合,K28.5分别把28和5换成二进制,然后放一起,再重新组合,低三位101放前面,高五位放后面,那不就成8‘b10111100即8’hBC了吗,以此类推,其他的k码怎么算你就知道了。关于k码换算,你得去看文章,我这里只是让你简单了解一下,别迷糊了,BC是怎么来的不知道!!!

我的编码顺序:

1.等待有效数据的到来,这个过程一直向链路发送空闲码,训练链路

2.等有效数据来了发送帧头,进行编码

3.开始发送有效数据(此项目我发送的是顺序数据,但是我在代码中预留了关键握手信号vld和rdy,有需要的同学后期自己在我的代码上面改就行了)

4.有效数据发送完成,进行编码

5.发送帧尾进行编码

6.接着发送空闲码进行编码

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: FPGA NXH

//

// Create Date: 2025/06/09 11:06:10

// Design Name:

// Module Name: user_gtx_tx

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module user_gtx_tx#

(

parameter DATA_WIDTH = 32,

parameter KCHAR_WIDTH = 4

)

(

input clk,

input rstn,

input sys_on,

input tx0_clk,

input tx0_link,

output [DATA_WIDTH-1:0] tx0_data,

output [KCHAR_WIDTH-1:0] tx0_kdata,

input tx1_clk,

input tx1_link,

output [DATA_WIDTH-1:0] tx1_data,

output [KCHAR_WIDTH-1:0] tx1_kdata

);

//------------parameter------------------------------

localparam K_CHAR_VLD = 4'h0001;

localparam K_CHAR_NVLD = 4'h0000;

localparam FRAM_IDLE = 32'h55_AA_00_BC; //空闲码

localparam FRAM_SOF = 32'h55_AA_FF_BC; //帧头

localparam FRAM_COM = 32'h55_AA_DD_BC; //有效数据发送完毕

localparam FRAM_EOF = 32'h55_AA_EE_BC; //帧尾

//------------register-------------------------------

reg [DATA_WIDTH-1:0] cnt_data;

reg [DATA_WIDTH-1:0] cnt_data_r=16'h0;

reg cnt_data_vld;

//-----------------预留------------------------------

wire rx_data_rdy;

reg tx0_data_r_vld;

//---------------------------------------------------

reg [DATA_WIDTH-1:0] tx0_data_r;

reg [DATA_WIDTH-1:0] tx1_data_r;

reg [KCHAR_WIDTH-1:0] tx0_kdata_r;

reg [KCHAR_WIDTH-1:0] tx1_kdata_r;

reg [3:0] tx0_link_r;

reg [3:0] tx1_link_r;

//------------status----------------------------------

reg [3:0] state_cur;

reg [3:0] state_next;

//------------------link_r-----------------------------

always @ (posedge tx0_clk) tx0_link_r <= {tx0_link_r[2:0], tx0_link};

always @ (posedge tx1_clk) tx1_link_r <= {tx1_link_r[2:0], tx1_link};

//---------------------预留-----------------------------

assign rx_data_rdy = (state_cur == 'h1|| state_cur == 'h2) ? 1'h1 : 1'h0;

//------------------------------------------------------

always @ (posedge tx0_clk) begin

if (!tx0_link_r[3]) begin

cnt_data <= 'h0;

cnt_data_vld <= 'h0;

end else if ((state_cur == 'h1|| state_cur == 'h2) && state_next != 'h3 && cnt_data <= 32'h0000_00FF) begin

cnt_data <= cnt_data + 'h1;

cnt_data_vld <= 'h1;

end else begin

cnt_data <= 'h0;

cnt_data_vld <= 'h0;

end

end

always @ (posedge tx0_clk) cnt_data_r <= cnt_data;

//------------------status------------------------------

always @ (posedge tx0_clk) begin

if (!tx0_link_r[3])

state_cur <= 'h0;

else

state_cur <= state_next;

end

always @ (*) begin

state_next = state_cur;

case (state_cur)

'h0 : begin

if (sys_on)

if (tx0_link_r[3])

state_next = 'h1;

else

state_next = 'h0;

else

state_next = 'h0;

end

'h1 : state_next = 'h2;

'h2 : begin

if (cnt_data_vld) begin

state_next = 'h2;

end else begin

state_next = 'h3;

end

end

'h3 : state_next = 'h4;

'h4 : state_next = 'h0;

default : state_next = 'h4;

endcase

end

always @ (posedge tx0_clk) begin

if (!tx0_link_r[3]) begin

tx0_data_r <= 'h0;

tx0_kdata_r <= 'h0;

end else begin

case (state_cur)

'h0 : begin

tx0_data_r <= FRAM_IDLE; //发送空闲码

tx0_kdata_r <= 4'b0001;

end

'h1 : begin

tx0_data_r <= FRAM_SOF; //发送帧头

tx0_kdata_r <= K_CHAR_VLD;

end

'h2 : begin

if (cnt_data_vld) begin //发送有效数据包

tx0_data_r <= cnt_data_r;

tx0_kdata_r <= K_CHAR_NVLD;

end else begin

tx0_data_r <= FRAM_COM; //有效数据包发送完毕

tx0_kdata_r <= K_CHAR_VLD;

end

end

'h3 : begin

tx0_data_r <= FRAM_EOF; //发送帧尾

tx0_kdata_r <= K_CHAR_VLD;

end

'h4 : begin //发送空闲码

tx0_data_r <= FRAM_IDLE;

tx0_kdata_r <= K_CHAR_VLD;

end

default : ;

endcase

end

end

//------------------预留-------------------------------

always @ (posedge tx0_clk) begin

if (!tx0_link_r[3])

tx0_data_r_vld <= 'h0;

else if (state_cur == 'h2 && cnt_data_vld) //这个地方的cnt_data_vld最后可以换成实际的data_vld即可

tx0_data_r_vld <= 'h1;

else

tx0_data_r_vld <= 'h0;

end

//------------------output port------------------------

assign tx0_data = tx0_data_r;

assign tx0_kdata = tx0_kdata_r;

assign tx1_data = tx1_link_r[3] ? tx0_data_r : 'h0;

assign tx1_kdata = tx1_link_r[3] ? tx0_kdata_r : 'h0;

//----------------------DEBUG-----------------------

ila_0 ILA_user_tx (

.clk (tx0_clk), // input wire clk

.probe0 ({

'h0,

sys_on,

sys_on_r,

cnt_data[31:0], //32

cnt_data_r,

cnt_data_vld,

tx0_data_r_vld,

state_cur, //4

state_next, //4

tx0_link_r, //4

tx1_link_r, //4

tx0_data_r, //32

tx0_kdata_r //32

}) // input wire [255:0] probe0

);

endmodule

解包解码:

心善的我再提示一下:解码出来的时钟域最后你得换成你自己的系统时钟域,不太明白的同学就又问了,怎么换时钟域啊啊啊啊啊,还能怎么换,异步fifo,用爆FPGA芯片资源,用就行了。此项目我没转换红红火火恍恍惚惚

解码思路:

根据自己定制的编码协议进行解码

1.先解数据帧头

2.得到有效数据

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: FPGA NXH

//

// Create Date: 2025/06/09 11:06:47

// Design Name:

// Module Name: user_gtx_rx

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module user_gtx_rx #

(

parameter DATA_WIDTH = 32,

parameter KCHAR_WIDTH = 4

)

(

input clk,

input rstn,

input rx0_clk,

input rx0_link,

input [DATA_WIDTH-1:0] rx0_data,

input [KCHAR_WIDTH-1:0] rx0_kdata,

input rx1_clk,

input rx1_link,

input [DATA_WIDTH-1:0] rx1_data,

input [KCHAR_WIDTH-1:0] rx1_kdata,

output [DATA_WIDTH-1:0] user_rx0_data,

output user_rx0_data_vld,

output [DATA_WIDTH-1:0] user_rx1_data,

output user_rx1_data_vld

);

//------------paramerter-----------------------------

localparam FRAM_SOF = 32'h55_AA_FF_BC; //帧头

localparam FRAM_EOF = 32'h55_AA_EE_BC; //帧尾

//------------register-------------------------------

reg [DATA_WIDTH-1:0] rx0_data_r =0;

reg [DATA_WIDTH-1:0] rx1_data_r =0;

reg [DATA_WIDTH-1:0] rx0_data_1r=0;

reg [DATA_WIDTH-1:0] rx1_data_1r=0;

reg [DATA_WIDTH-1:0] rx0_data_2r=0;

reg [DATA_WIDTH-1:0] rx1_data_2r=0;

reg [KCHAR_WIDTH-1:0] rx0_kdata_r ='h0;

reg [KCHAR_WIDTH-1:0] rx1_kdata_r ='h0;

reg [KCHAR_WIDTH-1:0] rx0_kdata_1r='h0;

reg [KCHAR_WIDTH-1:0] rx1_kdata_1r='h0;

reg [KCHAR_WIDTH-1:0] rx0_kdata_2r='h0;

reg [KCHAR_WIDTH-1:0] rx1_kdata_2r='h0;

reg [3:0] rx0_link_r;

reg [3:0] rx1_link_r;

reg [DATA_WIDTH-1:0] user_data;

reg user_data_vld;

reg sof_vld;

reg eof_vld;

reg frame_vld;

reg [2:0] state_cur;

reg [2:0] state_next;

//------------------link_r buffer---------------------------

always @ (posedge rx0_clk) rx0_link_r <= {rx0_link_r[2:0], rx0_link};

always @ (posedge rx1_clk) rx1_link_r <= {rx1_link_r[2:0], rx1_link};

//------------------data buffer-----------------------------

always @ (posedge rx0_clk) begin

rx0_data_r <= rx0_data;

rx0_data_1r <= rx0_data_r;

rx0_data_2r <= rx0_data_1r;

rx1_data_r <= rx1_data;

rx1_data_1r <= rx1_data_r;

rx1_data_2r <= rx1_data_1r;

end

always @ (posedge rx0_clk) begin

rx0_kdata_r <= rx0_kdata;

rx0_kdata_1r <= rx0_kdata_r;

rx0_kdata_2r <= rx0_kdata_1r;

rx1_kdata_r <= rx1_kdata;

rx1_kdata_1r <= rx1_kdata_r;

rx1_kdata_2r <= rx1_kdata_1r;

end

always @ (posedge rx0_clk) begin

if (!rx0_link_r[3]) begin

sof_vld <= 'h0;

end else if (rx0_data_r==FRAM_SOF && rx0_kdata_r=='h1) begin

sof_vld <= 'h1;

end else begin

sof_vld <= 'h0;

end

end

always @ (posedge rx0_clk) begin

if (!rx0_link_r[3]) begin

eof_vld <= 'h0;

end else if (rx0_data_r==FRAM_EOF && rx0_kdata_r=='h1) begin

eof_vld <= 'h1;

end else begin

eof_vld <= 'h0;

end

end

always @ (posedge rx0_clk) begin

if (!rx0_link_r[3]) begin

frame_vld <= 'h0;

end else if (sof_vld || eof_vld) begin

frame_vld <= 'h0;

end else begin

frame_vld <= 'h1;

end

end

always @ (posedge rx0_clk) begin

if (!rx0_link_r[3]) begin

user_data <= 'h0;

user_data_vld <= 'h0;

end else if (rx0_kdata_2r=='h0 && frame_vld) begin

user_data <= rx0_data_2r;

user_data_vld <= 'h1;

end else begin

user_data <= user_data;

user_data_vld <= 'h0;

end

end

//-------------------output port---------------------

assign user_rx0_data = user_data;

assign user_rx0_data_vld = user_data_vld;

assign user_rx1_data = rx1_link_r[3] ? user_data : 'h0;

assign user_rx1_data_vld = rx1_link_r[3] ? user_data_vld : 'h0;

//----------------------DEBUG-----------------------

ila_0 ILA_user_rx (

.clk (rx0_clk), // input wire clk

.probe0 ({

'h0,

rx0_data,

rx0_kdata,

sof_vld,

eof_vld,

frame_vld,

// state_cur,

// state_next,

rx0_link_r,

rx1_link_r,

rx0_data_r,

rx0_kdata_r,

rx0_data_1r,

rx0_kdata_1r,

rx0_data_2r,

rx0_kdata_2r,

user_data,

user_data_vld

}) // input wire [255:0] probe0

);

endmodule

GT收发顶层:

这个模块中,你得把原有的帧生成模块和帧检查模块屏蔽掉使用!!!!里面还有的参数进行了修改,同学们自己看源码即可。

////////////////////////////////////////////////////////////////////////////////

// ____ ____

// / /\/ /

// /___/ \ / Vendor: Xilinx

// \ \ \/ Version : 3.6

// \ \ Application : 7 Series FPGAs Transceivers Wizard

// / / Filename : gtx_aurora_x2_exdes.v

// /___/ /\

// \ \ / \

// \___\/\___\

//

//

// Module gtx_aurora_x2_exdes

// Generated by Xilinx 7 Series FPGAs Transceivers Wizard

//

//

// (c) Copyright 2010-2012 Xilinx, Inc. All rights reserved.

//

// This file contains confidential and proprietary information

// of Xilinx, Inc. and is protected under U.S. and

// international copyright and other intellectual property

// laws.

//

// DISCLAIMER

// This disclaimer is not a license and does not grant any

// rights to the materials distributed herewith. Except as

// otherwise provided in a valid license issued to you by

// Xilinx, and to the maximum extent permitted by applicable

// law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND

// WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES

// AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING

// BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-

// INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and

// (2) Xilinx shall not be liable (whether in contract or tort,

// including negligence, or under any other theory of

// liability) for any loss or damage of any kind or nature

// related to, arising under or in connection with these

// materials, including for any direct, or any indirect,

// special, incidental, or consequential loss or damage

// (including loss of data, profits, goodwill, or any type of

// loss or damage suffered as a result of any action brought

// by a third party) even if such damage or loss was

// reasonably foreseeable or Xilinx had been advised of the

// possibility of the same.

//

// CRITICAL APPLICATIONS

// Xilinx products are not designed or intended to be fail-

// safe, or for use in any application requiring fail-safe

// performance, such as life-support or safety devices or

// systems, Class III medical devices, nuclear facilities,

// applications related to the deployment of airbags, or any

// other applications that could lead to death, personal

// injury, or severe property or environmental damage

// (individually and collectively, "Critical

// Applications"). Customer assumes the sole risk and

// liability of any use of Xilinx products in Critical

// Applications, subject only to applicable laws and

// regulations governing limitations on product liability.

//

// THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS

// PART OF THIS FILE AT ALL TIMES.

`timescale 1ns / 1ps

`define DLY #1

(* DowngradeIPIdentifiedWarnings="yes" *)

//***********************************Entity Declaration************************

(* CORE_GENERATION_INFO = "gtx_aurora_x2,gtwizard_v3_6_11,{protocol_file=aurora_8b10b_single_lane_4byte}" *)

module gtx_aurora_x2_exdes #

(

parameter EXAMPLE_CONFIG_INDEPENDENT_LANES = 1,//configuration for frame gen and check

parameter EXAMPLE_LANE_WITH_START_CHAR = 0, // specifies lane with unique start frame char

parameter EXAMPLE_WORDS_IN_BRAM = 512, // specifies amount of data in BRAM

parameter EXAMPLE_SIM_GTRESET_SPEEDUP = "TRUE", // simulation setting for GT SecureIP model

parameter EXAMPLE_USE_CHIPSCOPE = 0, // Set to 1 to use Chipscope to drive resets

parameter STABLE_CLOCK_PERIOD = 10

)

(

input wire Q1_CLK1_GTREFCLK_PAD_N_IN,

input wire Q1_CLK1_GTREFCLK_PAD_P_IN,

input wire DRP_CLK_IN,

input wire [1:0] RXN_IN,

input wire [1:0] RXP_IN,

output wire [1:0] TXN_OUT,

output wire [1:0] TXP_OUT,

//-------------user interface-------------------------

input soft_rst_tx,

input soft_rst_rx,

input [2:0] gt_loopback,

output user_rx0_clk,

output [31:0] user_rx0_data,

output [3:0] user_rx0_kdata,

output user_rx0_link,

output user_rx1_clk,

output [31:0] user_rx1_data,

output [3:0] user_rx1_kdata,

output user_rx1_link,

output user_tx0_clk,

input [31:0] user_tx0_data,

input [3:0] user_tx0_kdata,

output user_tx0_link,

output user_tx1_clk,

input [31:0] user_tx1_data,

input [3:0] user_tx1_kdata,

output user_tx1_link

);

wire soft_reset_i;

(*mark_debug = "TRUE" *) wire soft_reset_vio_i;

//************************** Register Declarations ****************************

wire gt_txfsmresetdone_i;

wire gt_rxfsmresetdone_i;

(* ASYNC_REG = "TRUE" *)reg gt_txfsmresetdone_r;

(* ASYNC_REG = "TRUE" *)reg gt_txfsmresetdone_r2;

wire gt0_txfsmresetdone_i;

wire gt0_rxfsmresetdone_i;

(* ASYNC_REG = "TRUE" *)reg gt0_txfsmresetdone_r;

(* ASYNC_REG = "TRUE" *)reg gt0_txfsmresetdone_r2;

(* ASYNC_REG = "TRUE" *)reg gt0_rxfsmresetdone_r;

(* ASYNC_REG = "TRUE" *)reg gt0_rxfsmresetdone_r2;

(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_r;

(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_r2;

(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_r3;

(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_vio_r;

(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_vio_r2;

(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_vio_r3;

wire gt1_txfsmresetdone_i;

wire gt1_rxfsmresetdone_i;

(* ASYNC_REG = "TRUE" *)reg gt1_txfsmresetdone_r;

(* ASYNC_REG = "TRUE" *)reg gt1_txfsmresetdone_r2;

(* ASYNC_REG = "TRUE" *)reg gt1_rxfsmresetdone_r;

(* ASYNC_REG = "TRUE" *)reg gt1_rxfsmresetdone_r2;

(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_r;

(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_r2;

(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_r3;

(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_vio_r;

(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_vio_r2;

(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_vio_r3;

reg [5:0] reset_counter = 0;

reg [3:0] reset_pulse;

//**************************** Wire Declarations ******************************//

//------------------------ GT Wrapper Wires ------------------------------

//________________________________________________________________________

//________________________________________________________________________

//GT0 (X1Y5)

//------------------------------- CPLL Ports -------------------------------

wire gt0_cpllfbclklost_i;

wire gt0_cplllock_i;

wire gt0_cpllrefclklost_i;

wire gt0_cpllreset_i;

//-------------------------- Channel - DRP Ports --------------------------

wire [8:0] gt0_drpaddr_i;

wire [15:0] gt0_drpdi_i;

wire [15:0] gt0_drpdo_i;

wire gt0_drpen_i;

wire gt0_drprdy_i;

wire gt0_drpwe_i;

//------------------------- Digital Monitor Ports --------------------------

wire [7:0] gt0_dmonitorout_i;

//----------------------------- Loopback Ports -----------------------------

wire [2:0] gt0_loopback_i;

//---------------------------- Power-Down Ports ----------------------------

wire [1:0] gt0_rxpd_i;

wire [1:0] gt0_txpd_i;

//------------------- RX Initialization and Reset Ports --------------------

wire gt0_eyescanreset_i;

wire gt0_rxuserrdy_i;

//------------------------ RX Margin Analysis Ports ------------------------

wire gt0_eyescandataerror_i;

wire gt0_eyescantrigger_i;

//----------------------- Receive Ports - CDR Ports ------------------------

wire gt0_rxcdrhold_i;

wire gt0_rxcdrovrden_i;

//----------------- Receive Ports - Clock Correction Ports -----------------

wire [1:0] gt0_rxclkcorcnt_i;

//---------------- Receive Ports - FPGA RX interface Ports -----------------

wire [31:0] gt0_rxdata_i;

//----------------- Receive Ports - Pattern Checker Ports ------------------

wire gt0_rxprbserr_i;

wire [2:0] gt0_rxprbssel_i;

//----------------- Receive Ports - Pattern Checker ports ------------------

wire gt0_rxprbscntreset_i;

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

wire [3:0] gt0_rxdisperr_i;

wire [3:0] gt0_rxnotintable_i;

//------------------------- Receive Ports - RX AFE -------------------------

wire gt0_gtxrxp_i;

//---------------------- Receive Ports - RX AFE Ports ----------------------

wire gt0_gtxrxn_i;

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

wire gt0_rxbufreset_i;

wire [2:0] gt0_rxbufstatus_i;

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

wire gt0_rxbyteisaligned_i;

wire gt0_rxbyterealign_i;

wire gt0_rxcommadet_i;

wire gt0_rxmcommaalignen_i;

wire gt0_rxpcommaalignen_i;

//------------------- Receive Ports - RX Equalizer Ports -------------------

wire gt0_rxdfelpmreset_i;

wire [6:0] gt0_rxmonitorout_i;

wire [1:0] gt0_rxmonitorsel_i;

//------------- Receive Ports - RX Fabric Output Control Ports -------------

wire gt0_rxoutclk_i;

wire gt0_rxoutclkfabric_i;

//----------- Receive Ports - RX Initialization and Reset Ports ------------

wire gt0_gtrxreset_i;

wire gt0_rxpcsreset_i;

wire gt0_rxpmareset_i;

//---------------- Receive Ports - RX Margin Analysis ports ----------------

wire gt0_rxlpmen_i;

//--------------- Receive Ports - RX Polarity Control Ports ----------------

wire gt0_rxpolarity_i;

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

wire [3:0] gt0_rxchariscomma_i;

wire [3:0] gt0_rxcharisk_i;

//------------ Receive Ports -RX Initialization and Reset Ports ------------

wire gt0_rxresetdone_i;

//---------------------- TX Configurable Driver Ports ----------------------

wire [4:0] gt0_txpostcursor_i;

wire [4:0] gt0_txprecursor_i;

//------------------- TX Initialization and Reset Ports --------------------

wire gt0_gttxreset_i;

wire gt0_txuserrdy_i;

//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------

wire [3:0] gt0_txchardispmode_i;

wire [3:0] gt0_txchardispval_i;

//---------------- Transmit Ports - Pattern Generator Ports ----------------

wire gt0_txprbsforceerr_i;

//-------------------- Transmit Ports - TX Buffer Ports --------------------

wire [1:0] gt0_txbufstatus_i;

//------------- Transmit Ports - TX Configurable Driver Ports --------------

wire [3:0] gt0_txdiffctrl_i;

wire [6:0] gt0_txmaincursor_i;

//---------------- Transmit Ports - TX Data Path interface -----------------

wire [31:0] gt0_txdata_i;

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

wire gt0_gtxtxn_i;

wire gt0_gtxtxp_i;

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

wire gt0_txoutclk_i;

wire gt0_txoutclkfabric_i;

wire gt0_txoutclkpcs_i;

//------------------- Transmit Ports - TX Gearbox Ports --------------------

wire [3:0] gt0_txcharisk_i;

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

wire gt0_txpcsreset_i;

wire gt0_txpmareset_i;

wire gt0_txresetdone_i;

//--------------- Transmit Ports - TX Polarity Control Ports ---------------

wire gt0_txpolarity_i;

//---------------- Transmit Ports - pattern Generator Ports ----------------

wire [2:0] gt0_txprbssel_i;

//________________________________________________________________________

//________________________________________________________________________

//GT1 (X1Y6)

//------------------------------- CPLL Ports -------------------------------

wire gt1_cpllfbclklost_i;

wire gt1_cplllock_i;

wire gt1_cpllrefclklost_i;

wire gt1_cpllreset_i;

//-------------------------- Channel - DRP Ports --------------------------

wire [8:0] gt1_drpaddr_i;

wire [15:0] gt1_drpdi_i;

wire [15:0] gt1_drpdo_i;

wire gt1_drpen_i;

wire gt1_drprdy_i;

wire gt1_drpwe_i;

//------------------------- Digital Monitor Ports --------------------------

wire [7:0] gt1_dmonitorout_i;

//----------------------------- Loopback Ports -----------------------------

wire [2:0] gt1_loopback_i;

//---------------------------- Power-Down Ports ----------------------------

wire [1:0] gt1_rxpd_i;

wire [1:0] gt1_txpd_i;

//------------------- RX Initialization and Reset Ports --------------------

wire gt1_eyescanreset_i;

wire gt1_rxuserrdy_i;

//------------------------ RX Margin Analysis Ports ------------------------

wire gt1_eyescandataerror_i;

wire gt1_eyescantrigger_i;

//----------------------- Receive Ports - CDR Ports ------------------------

wire gt1_rxcdrhold_i;

wire gt1_rxcdrovrden_i;

//----------------- Receive Ports - Clock Correction Ports -----------------

wire [1:0] gt1_rxclkcorcnt_i;

//---------------- Receive Ports - FPGA RX interface Ports -----------------

wire [31:0] gt1_rxdata_i;

//----------------- Receive Ports - Pattern Checker Ports ------------------

wire gt1_rxprbserr_i;

wire [2:0] gt1_rxprbssel_i;

//----------------- Receive Ports - Pattern Checker ports ------------------

wire gt1_rxprbscntreset_i;

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

wire [3:0] gt1_rxdisperr_i;

wire [3:0] gt1_rxnotintable_i;

//------------------------- Receive Ports - RX AFE -------------------------

wire gt1_gtxrxp_i;

//---------------------- Receive Ports - RX AFE Ports ----------------------

wire gt1_gtxrxn_i;

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

wire gt1_rxbufreset_i;

wire [2:0] gt1_rxbufstatus_i;

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

wire gt1_rxbyteisaligned_i;

wire gt1_rxbyterealign_i;

wire gt1_rxcommadet_i;

wire gt1_rxmcommaalignen_i;

wire gt1_rxpcommaalignen_i;

//------------------- Receive Ports - RX Equalizer Ports -------------------

wire gt1_rxdfelpmreset_i;

wire [6:0] gt1_rxmonitorout_i;

wire [1:0] gt1_rxmonitorsel_i;

//------------- Receive Ports - RX Fabric Output Control Ports -------------

wire gt1_rxoutclk_i;

wire gt1_rxoutclkfabric_i;

//----------- Receive Ports - RX Initialization and Reset Ports ------------

wire gt1_gtrxreset_i;

wire gt1_rxpcsreset_i;

wire gt1_rxpmareset_i;

//---------------- Receive Ports - RX Margin Analysis ports ----------------

wire gt1_rxlpmen_i;

//--------------- Receive Ports - RX Polarity Control Ports ----------------

wire gt1_rxpolarity_i;

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

wire [3:0] gt1_rxchariscomma_i;

wire [3:0] gt1_rxcharisk_i;

//------------ Receive Ports -RX Initialization and Reset Ports ------------

wire gt1_rxresetdone_i;

//---------------------- TX Configurable Driver Ports ----------------------

wire [4:0] gt1_txpostcursor_i;

wire [4:0] gt1_txprecursor_i;

//------------------- TX Initialization and Reset Ports --------------------

wire gt1_gttxreset_i;

wire gt1_txuserrdy_i;

//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------

wire [3:0] gt1_txchardispmode_i;

wire [3:0] gt1_txchardispval_i;

//---------------- Transmit Ports - Pattern Generator Ports ----------------

wire gt1_txprbsforceerr_i;

//-------------------- Transmit Ports - TX Buffer Ports --------------------

wire [1:0] gt1_txbufstatus_i;

//------------- Transmit Ports - TX Configurable Driver Ports --------------

wire [3:0] gt1_txdiffctrl_i;

wire [6:0] gt1_txmaincursor_i;

//---------------- Transmit Ports - TX Data Path interface -----------------

wire [31:0] gt1_txdata_i;

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

wire gt1_gtxtxn_i;

wire gt1_gtxtxp_i;

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

wire gt1_txoutclk_i;

wire gt1_txoutclkfabric_i;

wire gt1_txoutclkpcs_i;

//------------------- Transmit Ports - TX Gearbox Ports --------------------

wire [3:0] gt1_txcharisk_i;

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

wire gt1_txpcsreset_i;

wire gt1_txpmareset_i;

wire gt1_txresetdone_i;

//--------------- Transmit Ports - TX Polarity Control Ports ---------------

wire gt1_txpolarity_i;

//---------------- Transmit Ports - pattern Generator Ports ----------------

wire [2:0] gt1_txprbssel_i;

//____________________________COMMON PORTS________________________________

//-------------------- Common Block - Ref Clock Ports ---------------------

wire gt0_gtrefclk1_common_i;

//----------------------- Common Block - QPLL Ports ------------------------

wire gt0_qplllock_i;

wire gt0_qpllrefclklost_i;

wire gt0_qpllreset_i;

//----------------------------- Global Signals -----------------------------

wire drpclk_in_i;

wire DRPCLK_IN;

wire gt0_tx_system_reset_c;

wire gt0_rx_system_reset_c;

wire gt1_tx_system_reset_c;

wire gt1_rx_system_reset_c;

wire tied_to_ground_i;

wire [63:0] tied_to_ground_vec_i;

wire tied_to_vcc_i;

wire [7:0] tied_to_vcc_vec_i;

wire GTTXRESET_IN;

wire GTRXRESET_IN;

wire CPLLRESET_IN;

wire QPLLRESET_IN;

//--------------------------- User Clocks ---------------------------------

wire gt0_txusrclk_i;

wire gt0_txusrclk2_i;

wire gt0_rxusrclk_i;

wire gt0_rxusrclk2_i;

wire gt1_txusrclk_i;

wire gt1_txusrclk2_i;

wire gt1_rxusrclk_i;

wire gt1_rxusrclk2_i;

//--------------------------- Reference Clocks ----------------------------

wire q1_clk1_refclk_i;

//--------------------- Frame check/gen Module Signals --------------------

wire gt0_matchn_i;

wire [3:0] gt0_txcharisk_float_i;

wire [15:0] gt0_txdata_float16_i;

wire [31:0] gt0_txdata_float_i;

wire gt0_block_sync_i;

wire gt0_track_data_i;

wire [7:0] gt0_error_count_i;

wire gt0_frame_check_reset_i;

wire gt0_inc_in_i;

wire gt0_inc_out_i;

wire [31:0] gt0_unscrambled_data_i;

wire gt1_matchn_i;

wire [3:0] gt1_txcharisk_float_i;

wire [15:0] gt1_txdata_float16_i;

wire [31:0] gt1_txdata_float_i;

wire gt1_block_sync_i;

wire gt1_track_data_i;

wire [7:0] gt1_error_count_i;

wire gt1_frame_check_reset_i;

wire gt1_inc_in_i;

wire gt1_inc_out_i;

wire [31:0] gt1_unscrambled_data_i;

wire reset_on_data_error_i;

wire track_data_out_i;

//--------------------- Chipscope Signals ---------------------------------

(*mark_debug = "TRUE" *)wire rxresetdone_vio_i;

wire [35:0] tx_data_vio_control_i;

wire [35:0] rx_data_vio_control_i;

wire [35:0] shared_vio_control_i;

wire [35:0] ila_control_i;

wire [35:0] channel_drp_vio_control_i;

wire [35:0] common_drp_vio_control_i;

wire [31:0] tx_data_vio_async_in_i;

wire [31:0] tx_data_vio_sync_in_i;

wire [31:0] tx_data_vio_async_out_i;

wire [31:0] tx_data_vio_sync_out_i;

wire [31:0] rx_data_vio_async_in_i;

wire [31:0] rx_data_vio_sync_in_i;

wire [31:0] rx_data_vio_async_out_i;

wire [31:0] rx_data_vio_sync_out_i;

wire [31:0] shared_vio_in_i;

wire [31:0] shared_vio_out_i;

wire [163:0] ila_in_i;

wire [31:0] channel_drp_vio_async_in_i;

wire [31:0] channel_drp_vio_sync_in_i;

wire [31:0] channel_drp_vio_async_out_i;

wire [31:0] channel_drp_vio_sync_out_i;

wire [31:0] common_drp_vio_async_in_i;

wire [31:0] common_drp_vio_sync_in_i;

wire [31:0] common_drp_vio_async_out_i;

wire [31:0] common_drp_vio_sync_out_i;

wire [31:0] gt0_tx_data_vio_async_in_i;

wire [31:0] gt0_tx_data_vio_sync_in_i;

wire [31:0] gt0_tx_data_vio_async_out_i;

wire [31:0] gt0_tx_data_vio_sync_out_i;

wire [31:0] gt0_rx_data_vio_async_in_i;

wire [31:0] gt0_rx_data_vio_sync_in_i;

wire [31:0] gt0_rx_data_vio_async_out_i;

wire [31:0] gt0_rx_data_vio_sync_out_i;

wire [163:0] gt0_ila_in_i;

wire [31:0] gt0_channel_drp_vio_async_in_i;

wire [31:0] gt0_channel_drp_vio_sync_in_i;

wire [31:0] gt0_channel_drp_vio_async_out_i;

wire [31:0] gt0_channel_drp_vio_sync_out_i;

wire [31:0] gt0_common_drp_vio_async_in_i;

wire [31:0] gt0_common_drp_vio_sync_in_i;

wire [31:0] gt0_common_drp_vio_async_out_i;

wire [31:0] gt0_common_drp_vio_sync_out_i;

wire [31:0] gt1_tx_data_vio_async_in_i;

wire [31:0] gt1_tx_data_vio_sync_in_i;

wire [31:0] gt1_tx_data_vio_async_out_i;

wire [31:0] gt1_tx_data_vio_sync_out_i;

wire [31:0] gt1_rx_data_vio_async_in_i;

wire [31:0] gt1_rx_data_vio_sync_in_i;

wire [31:0] gt1_rx_data_vio_async_out_i;

wire [31:0] gt1_rx_data_vio_sync_out_i;

wire [163:0] gt1_ila_in_i;

wire [31:0] gt1_channel_drp_vio_async_in_i;

wire [31:0] gt1_channel_drp_vio_sync_in_i;

wire [31:0] gt1_channel_drp_vio_async_out_i;

wire [31:0] gt1_channel_drp_vio_sync_out_i;

wire [31:0] gt1_common_drp_vio_async_in_i;

wire [31:0] gt1_common_drp_vio_sync_in_i;

wire [31:0] gt1_common_drp_vio_async_out_i;

wire [31:0] gt1_common_drp_vio_sync_out_i;

wire gttxreset_i;

wire gtrxreset_i;

wire mux_sel_i;

wire user_tx_reset_i;

wire user_rx_reset_i;

wire tx_vio_clk_i;

wire tx_vio_clk_mux_out_i;

wire rx_vio_ila_clk_i;

wire rx_vio_ila_clk_mux_out_i;

wire cpllreset_i;

wire [(80 -32) -1:0] zero_vector_rx_80 ;

wire [(8 -4) -1:0] zero_vector_rx_8 ;

wire [79:0] gt0_rxdata_ila ;

wire [1:0] gt0_rxdatavalid_ila;

wire [7:0] gt0_rxcharisk_ila ;

wire gt0_txmmcm_lock_ila ;

wire gt0_rxmmcm_lock_ila ;

wire gt0_rxresetdone_ila ;

wire gt0_txresetdone_ila ;

wire [79:0] gt1_rxdata_ila ;

wire [1:0] gt1_rxdatavalid_ila;

wire [7:0] gt1_rxcharisk_ila ;

wire gt1_txmmcm_lock_ila ;

wire gt1_rxmmcm_lock_ila ;

wire gt1_rxresetdone_ila ;

wire gt1_txresetdone_ila ;

//**************************** Main Body of Code *******************************

// Static signal Assigments

assign tied_to_ground_i = 1'b0;

assign tied_to_ground_vec_i = 64'h0000000000000000;

assign tied_to_vcc_i = 1'b1;

assign tied_to_vcc_vec_i = 8'hff;

assign zero_vector_rx_80 = 0;

assign zero_vector_rx_8 = 0;

assign q1_clk1_refclk_i = 1'b0;

//------------------------------USER INTERFACE---------------------------

//-------------channel 0---------------------

assign user_rx0_clk = gt0_rxusrclk2_i;

assign user_rx0_data = gt0_rxdata_i;

assign user_rx0_kdata = gt0_rxcharisk_i;

assign user_rx0_link = gt0_rxfsmresetdone_i;

assign user_tx0_clk = gt0_txusrclk2_i;

assign gt0_txdata_i = user_tx0_data;

assign gt0_txcharisk_i = user_tx0_kdata;

assign user_tx0_link = gt0_txfsmresetdone_i;

//-------------channel 1---------------------

assign user_rx1_clk = gt1_rxusrclk2_i;

assign user_rx1_data = gt1_rxdata_i;

assign user_rx1_kdata = gt1_rxcharisk_i;

assign user_rx1_link = gt1_rxfsmresetdone_i;

assign user_tx1_clk = gt1_txusrclk2_i;

assign gt1_txdata_i = user_tx1_data;

assign gt1_txcharisk_i = user_tx1_kdata;

assign user_tx1_link = gt1_txfsmresetdone_i;

//***********************************************************************//

// //

//--------------------------- The GT Wrapper ----------------------------//

// //

//***********************************************************************//

// Use the instantiation template in the example directory to add the GT wrapper to your design.

// In this example, the wrapper is wired up for basic operation with a frame generator and frame

// checker. The GTs will reset, then attempt to align and transmit data. If channel bonding is

// enabled, bonding should occur after alignment.

// While connecting the GT TX/RX Reset ports below, please add a delay of

// minimum 500ns as mentioned in AR 43482.

gtx_aurora_x2_support #

(

.EXAMPLE_SIM_GTRESET_SPEEDUP (EXAMPLE_SIM_GTRESET_SPEEDUP),

.STABLE_CLOCK_PERIOD (STABLE_CLOCK_PERIOD)

)

gtx_aurora_x2_support_i

(

.soft_reset_tx_in (soft_rst_tx),

.soft_reset_rx_in (soft_rst_rx),

.dont_reset_on_data_error_in (tied_to_ground_i),

.q1_clk1_gtrefclk_pad_n_in(Q1_CLK1_GTREFCLK_PAD_N_IN),

.q1_clk1_gtrefclk_pad_p_in(Q1_CLK1_GTREFCLK_PAD_P_IN),

.gt0_tx_fsm_reset_done_out (gt0_txfsmresetdone_i),

.gt0_rx_fsm_reset_done_out (gt0_rxfsmresetdone_i),

.gt0_data_valid_in ('b1),

.gt1_tx_fsm_reset_done_out (gt1_txfsmresetdone_i),

.gt1_rx_fsm_reset_done_out (gt1_rxfsmresetdone_i),

.gt1_data_valid_in ('b1),

.gt0_txusrclk_out(gt0_txusrclk_i),

.gt0_txusrclk2_out(gt0_txusrclk2_i),

.gt0_rxusrclk_out(gt0_rxusrclk_i),

.gt0_rxusrclk2_out(gt0_rxusrclk2_i),

.gt1_txusrclk_out(gt1_txusrclk_i),

.gt1_txusrclk2_out(gt1_txusrclk2_i),

.gt1_rxusrclk_out(gt1_rxusrclk_i),

.gt1_rxusrclk2_out(gt1_rxusrclk2_i),

//_____________________________________________________________________

//_____________________________________________________________________

//GT0 (X1Y5)

//------------------------------- CPLL Ports -------------------------------

.gt0_cpllfbclklost_out (gt0_cpllfbclklost_i),

.gt0_cplllock_out (gt0_cplllock_i),

.gt0_cpllreset_in (tied_to_ground_i),

//-------------------------- Channel - DRP Ports --------------------------

.gt0_drpaddr_in (gt0_drpaddr_i),

.gt0_drpdi_in (gt0_drpdi_i),

.gt0_drpdo_out (gt0_drpdo_i),

.gt0_drpen_in (gt0_drpen_i),

.gt0_drprdy_out (gt0_drprdy_i),

.gt0_drpwe_in (gt0_drpwe_i),

//------------------------- Digital Monitor Ports --------------------------

.gt0_dmonitorout_out (gt0_dmonitorout_i),

//----------------------------- Loopback Ports -----------------------------

.gt0_loopback_in (gt_loopback),

//---------------------------- Power-Down Ports ----------------------------

.gt0_rxpd_in (gt0_rxpd_i),

.gt0_txpd_in (gt0_txpd_i),

//------------------- RX Initialization and Reset Ports --------------------

.gt0_eyescanreset_in (tied_to_ground_i),

.gt0_rxuserrdy_in (tied_to_vcc_i),

//------------------------ RX Margin Analysis Ports ------------------------

.gt0_eyescandataerror_out (gt0_eyescandataerror_i),

.gt0_eyescantrigger_in (tied_to_ground_i),

//----------------------- Receive Ports - CDR Ports ------------------------

.gt0_rxcdrhold_in (gt0_rxcdrhold_i),

.gt0_rxcdrovrden_in (tied_to_ground_i),

//----------------- Receive Ports - Clock Correction Ports -----------------

.gt0_rxclkcorcnt_out (gt0_rxclkcorcnt_i),

//---------------- Receive Ports - FPGA RX interface Ports -----------------

.gt0_rxdata_out (gt0_rxdata_i),

//----------------- Receive Ports - Pattern Checker Ports ------------------

.gt0_rxprbserr_out (gt0_rxprbserr_i),

.gt0_rxprbssel_in (gt0_rxprbssel_i),

//----------------- Receive Ports - Pattern Checker ports ------------------

.gt0_rxprbscntreset_in (gt0_rxprbscntreset_i),

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

.gt0_rxdisperr_out (gt0_rxdisperr_i),

.gt0_rxnotintable_out (gt0_rxnotintable_i),

//------------------------- Receive Ports - RX AFE -------------------------

.gt0_gtxrxp_in (RXP_IN[0]),

//---------------------- Receive Ports - RX AFE Ports ----------------------

.gt0_gtxrxn_in (RXN_IN[0]),

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

.gt0_rxbufreset_in (gt0_rxbufreset_i),

.gt0_rxbufstatus_out (gt0_rxbufstatus_i),

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

.gt0_rxbyteisaligned_out (gt0_rxbyteisaligned_i),

.gt0_rxbyterealign_out (gt0_rxbyterealign_i),

.gt0_rxcommadet_out (gt0_rxcommadet_i),

.gt0_rxmcommaalignen_in ('b1),

.gt0_rxpcommaalignen_in ('b1),

//------------------- Receive Ports - RX Equalizer Ports -------------------

.gt0_rxdfelpmreset_in (tied_to_ground_i),

.gt0_rxmonitorout_out (gt0_rxmonitorout_i),

.gt0_rxmonitorsel_in (2'b00),

//------------- Receive Ports - RX Fabric Output Control Ports -------------

.gt0_rxoutclkfabric_out (gt0_rxoutclkfabric_i),

//----------- Receive Ports - RX Initialization and Reset Ports ------------

.gt0_gtrxreset_in (tied_to_ground_i),

.gt0_rxpcsreset_in (tied_to_ground_i),

.gt0_rxpmareset_in (gt0_rxpmareset_i),

//---------------- Receive Ports - RX Margin Analysis ports ----------------

.gt0_rxlpmen_in (gt0_rxlpmen_i),

//--------------- Receive Ports - RX Polarity Control Ports ----------------

.gt0_rxpolarity_in (gt0_rxpolarity_i),

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

.gt0_rxchariscomma_out (gt0_rxchariscomma_i),

.gt0_rxcharisk_out (gt0_rxcharisk_i),

//------------ Receive Ports -RX Initialization and Reset Ports ------------

.gt0_rxresetdone_out (gt0_rxresetdone_i),

//---------------------- TX Configurable Driver Ports ----------------------

.gt0_txpostcursor_in (gt0_txpostcursor_i),

.gt0_txprecursor_in (gt0_txprecursor_i),

//------------------- TX Initialization and Reset Ports --------------------

.gt0_gttxreset_in (tied_to_ground_i),

.gt0_txuserrdy_in (tied_to_vcc_i),

//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------

.gt0_txchardispmode_in (gt0_txchardispmode_i),

.gt0_txchardispval_in (gt0_txchardispval_i),

//---------------- Transmit Ports - Pattern Generator Ports ----------------

.gt0_txprbsforceerr_in (gt0_txprbsforceerr_i),

//-------------------- Transmit Ports - TX Buffer Ports --------------------

.gt0_txbufstatus_out (gt0_txbufstatus_i),

//------------- Transmit Ports - TX Configurable Driver Ports --------------

.gt0_txdiffctrl_in (gt0_txdiffctrl_i),

.gt0_txmaincursor_in (7'b0000000),

//---------------- Transmit Ports - TX Data Path interface -----------------

.gt0_txdata_in (gt0_txdata_i),

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

.gt0_gtxtxn_out (TXN_OUT[0]),

.gt0_gtxtxp_out (TXP_OUT[0]),

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

.gt0_txoutclkfabric_out (gt0_txoutclkfabric_i),

.gt0_txoutclkpcs_out (gt0_txoutclkpcs_i),

//------------------- Transmit Ports - TX Gearbox Ports --------------------

.gt0_txcharisk_in (gt0_txcharisk_i),

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

.gt0_txpcsreset_in (tied_to_ground_i),

.gt0_txpmareset_in (tied_to_ground_i),

.gt0_txresetdone_out (gt0_txresetdone_i),

//--------------- Transmit Ports - TX Polarity Control Ports ---------------

.gt0_txpolarity_in (gt0_txpolarity_i),

//---------------- Transmit Ports - pattern Generator Ports ----------------

.gt0_txprbssel_in (gt0_txprbssel_i),

//_____________________________________________________________________

//_____________________________________________________________________

//GT1 (X1Y6)

//------------------------------- CPLL Ports -------------------------------

.gt1_cpllfbclklost_out (gt1_cpllfbclklost_i),

.gt1_cplllock_out (gt1_cplllock_i),

.gt1_cpllreset_in (tied_to_ground_i),

//-------------------------- Channel - DRP Ports --------------------------

.gt1_drpaddr_in (gt1_drpaddr_i),

.gt1_drpdi_in (gt1_drpdi_i),

.gt1_drpdo_out (gt1_drpdo_i),

.gt1_drpen_in (gt1_drpen_i),

.gt1_drprdy_out (gt1_drprdy_i),

.gt1_drpwe_in (gt1_drpwe_i),

//------------------------- Digital Monitor Ports --------------------------

.gt1_dmonitorout_out (gt1_dmonitorout_i),

//----------------------------- Loopback Ports -----------------------------

.gt1_loopback_in (gt1_loopback_i),

//---------------------------- Power-Down Ports ----------------------------

.gt1_rxpd_in (gt1_rxpd_i),

.gt1_txpd_in (gt1_txpd_i),

//------------------- RX Initialization and Reset Ports --------------------

.gt1_eyescanreset_in (tied_to_ground_i),

.gt1_rxuserrdy_in (tied_to_vcc_i),

//------------------------ RX Margin Analysis Ports ------------------------

.gt1_eyescandataerror_out (gt1_eyescandataerror_i),

.gt1_eyescantrigger_in (tied_to_ground_i),

//----------------------- Receive Ports - CDR Ports ------------------------

.gt1_rxcdrhold_in (gt1_rxcdrhold_i),

.gt1_rxcdrovrden_in (tied_to_ground_i),

//----------------- Receive Ports - Clock Correction Ports -----------------

.gt1_rxclkcorcnt_out (gt1_rxclkcorcnt_i),

//---------------- Receive Ports - FPGA RX interface Ports -----------------

.gt1_rxdata_out (gt1_rxdata_i),

//----------------- Receive Ports - Pattern Checker Ports ------------------

.gt1_rxprbserr_out (gt1_rxprbserr_i),

.gt1_rxprbssel_in (gt1_rxprbssel_i),

//----------------- Receive Ports - Pattern Checker ports ------------------

.gt1_rxprbscntreset_in (gt1_rxprbscntreset_i),

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

.gt1_rxdisperr_out (gt1_rxdisperr_i),

.gt1_rxnotintable_out (gt1_rxnotintable_i),

//------------------------- Receive Ports - RX AFE -------------------------

.gt1_gtxrxp_in (RXP_IN[1]),

//---------------------- Receive Ports - RX AFE Ports ----------------------

.gt1_gtxrxn_in (RXN_IN[1]),

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

.gt1_rxbufreset_in (gt1_rxbufreset_i),

.gt1_rxbufstatus_out (gt1_rxbufstatus_i),

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

.gt1_rxbyteisaligned_out (gt1_rxbyteisaligned_i),

.gt1_rxbyterealign_out (gt1_rxbyterealign_i),

.gt1_rxcommadet_out (gt1_rxcommadet_i),

.gt1_rxmcommaalignen_in ('b1),

.gt1_rxpcommaalignen_in ('b1),

//------------------- Receive Ports - RX Equalizer Ports -------------------

.gt1_rxdfelpmreset_in (tied_to_ground_i),

.gt1_rxmonitorout_out (gt1_rxmonitorout_i),

.gt1_rxmonitorsel_in (2'b00),

//------------- Receive Ports - RX Fabric Output Control Ports -------------

.gt1_rxoutclkfabric_out (gt1_rxoutclkfabric_i),

//----------- Receive Ports - RX Initialization and Reset Ports ------------

.gt1_gtrxreset_in (tied_to_ground_i),

.gt1_rxpcsreset_in (tied_to_ground_i),

.gt1_rxpmareset_in (gt1_rxpmareset_i),

//---------------- Receive Ports - RX Margin Analysis ports ----------------

.gt1_rxlpmen_in (gt1_rxlpmen_i),

//--------------- Receive Ports - RX Polarity Control Ports ----------------

.gt1_rxpolarity_in (gt1_rxpolarity_i),

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

.gt1_rxchariscomma_out (gt1_rxchariscomma_i),

.gt1_rxcharisk_out (gt1_rxcharisk_i),

//------------ Receive Ports -RX Initialization and Reset Ports ------------

.gt1_rxresetdone_out (gt1_rxresetdone_i),

//---------------------- TX Configurable Driver Ports ----------------------

.gt1_txpostcursor_in (gt1_txpostcursor_i),

.gt1_txprecursor_in (gt1_txprecursor_i),

//------------------- TX Initialization and Reset Ports --------------------

.gt1_gttxreset_in (tied_to_ground_i),

.gt1_txuserrdy_in (tied_to_vcc_i),

//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------

.gt1_txchardispmode_in (gt1_txchardispmode_i),

.gt1_txchardispval_in (gt1_txchardispval_i),

//---------------- Transmit Ports - Pattern Generator Ports ----------------

.gt1_txprbsforceerr_in (gt1_txprbsforceerr_i),

//-------------------- Transmit Ports - TX Buffer Ports --------------------

.gt1_txbufstatus_out (gt1_txbufstatus_i),

//------------- Transmit Ports - TX Configurable Driver Ports --------------

.gt1_txdiffctrl_in (gt1_txdiffctrl_i),

.gt1_txmaincursor_in (7'b0000000),

//---------------- Transmit Ports - TX Data Path interface -----------------

.gt1_txdata_in (gt1_txdata_i),

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

.gt1_gtxtxn_out (TXN_OUT[1]),

.gt1_gtxtxp_out (TXP_OUT[1]),

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

.gt1_txoutclkfabric_out (gt1_txoutclkfabric_i),

.gt1_txoutclkpcs_out (gt1_txoutclkpcs_i),

//------------------- Transmit Ports - TX Gearbox Ports --------------------

.gt1_txcharisk_in (gt1_txcharisk_i),

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

.gt1_txpcsreset_in (tied_to_ground_i),

.gt1_txpmareset_in (tied_to_ground_i),

.gt1_txresetdone_out (gt1_txresetdone_i),

//--------------- Transmit Ports - TX Polarity Control Ports ---------------

.gt1_txpolarity_in (gt1_txpolarity_i),

//---------------- Transmit Ports - pattern Generator Ports ----------------

.gt1_txprbssel_in (gt1_txprbssel_i),

//____________________________COMMON PORTS________________________________

.gt0_qplloutclk_out (),

.gt0_qplloutrefclk_out (),

.sysclk_in (DRP_CLK_IN)

);

// IBUFDS IBUFDS_DRP_CLK

// (

// .I (DRP_CLK_IN_P),

// .IB (DRP_CLK_IN_N),

// .O (DRPCLK_IN)

// );

// BUFG DRP_CLK_BUFG

// (

// .I (DRPCLK_IN),

// .O (drpclk_in_i)

// );

//***********************************************************************//

// //

//--------------------------- User Module Resets-------------------------//

// //

//***********************************************************************//

// All the User Modules i.e. FRAME_GEN, FRAME_CHECK and the sync modules

// are held in reset till the RESETDONE goes high.

// The RESETDONE is registered a couple of times on *USRCLK2 and connected

// to the reset of the modules

always @(posedge gt0_rxusrclk2_i or negedge gt0_rxresetdone_i)

begin

if (!gt0_rxresetdone_i)

begin

gt0_rxresetdone_r <= `DLY 1'b0;

gt0_rxresetdone_r2 <= `DLY 1'b0;

gt0_rxresetdone_r3 <= `DLY 1'b0;

end

else

begin

gt0_rxresetdone_r <= `DLY gt0_rxresetdone_i;

gt0_rxresetdone_r2 <= `DLY gt0_rxresetdone_r;

gt0_rxresetdone_r3 <= `DLY gt0_rxresetdone_r2;

end

end

always @(posedge gt0_txusrclk2_i or negedge gt0_txfsmresetdone_i)

begin

if (!gt0_txfsmresetdone_i)

begin

gt0_txfsmresetdone_r <= `DLY 1'b0;

gt0_txfsmresetdone_r2 <= `DLY 1'b0;

end

else

begin

gt0_txfsmresetdone_r <= `DLY gt0_txfsmresetdone_i;

gt0_txfsmresetdone_r2 <= `DLY gt0_txfsmresetdone_r;

end

end

always @(posedge gt1_rxusrclk2_i or negedge gt1_rxresetdone_i)

begin

if (!gt1_rxresetdone_i)

begin

gt1_rxresetdone_r <= `DLY 1'b0;

gt1_rxresetdone_r2 <= `DLY 1'b0;

gt1_rxresetdone_r3 <= `DLY 1'b0;

end

else

begin

gt1_rxresetdone_r <= `DLY gt1_rxresetdone_i;

gt1_rxresetdone_r2 <= `DLY gt1_rxresetdone_r;

gt1_rxresetdone_r3 <= `DLY gt1_rxresetdone_r2;

end

end

always @(posedge gt1_txusrclk2_i or negedge gt1_txfsmresetdone_i)

begin

if (!gt1_txfsmresetdone_i)

begin

gt1_txfsmresetdone_r <= `DLY 1'b0;

gt1_txfsmresetdone_r2 <= `DLY 1'b0;

end

else

begin

gt1_txfsmresetdone_r <= `DLY gt1_txfsmresetdone_i;

gt1_txfsmresetdone_r2 <= `DLY gt1_txfsmresetdone_r;

end

end

//***********************************************************************//

// //

//------------------------ Frame Generators ---------------------------//

// //

//***********************************************************************//

// The example design uses Block RAM based frame generators to provide test

// data to the GTs for transmission. By default the frame generators are

// loaded with an incrementing data sequence that includes commas/alignment

// characters for alignment. If your protocol uses channel bonding, the

// frame generator will also be preloaded with a channel bonding sequence.

// You can modify the data transmitted by changing the INIT values of the frame

// generator in this file. Pay careful attention to bit order and the spacing

// of your control and alignment characters.

// gtx_aurora_x2_GT_FRAME_GEN #

// (

// .WORDS_IN_BRAM(EXAMPLE_WORDS_IN_BRAM)

// )

// gt0_frame_gen

// (

// // User Interface

// .TX_DATA_OUT ({gt0_txdata_float_i,gt0_txdata_i,gt0_txdata_float16_i}),

// .TXCTRL_OUT ({gt0_txcharisk_float_i,gt0_txcharisk_i}),

// // System Interface

// .USER_CLK (gt0_txusrclk2_i),

// .SYSTEM_RESET (gt0_tx_system_reset_c)

// );

// gtx_aurora_x2_GT_FRAME_GEN #

// (

// .WORDS_IN_BRAM(EXAMPLE_WORDS_IN_BRAM)

// )

// gt1_frame_gen

// (

// // User Interface

// .TX_DATA_OUT ({gt1_txdata_float_i,gt1_txdata_i,gt1_txdata_float16_i}),

// .TXCTRL_OUT ({gt1_txcharisk_float_i,gt1_txcharisk_i}),

// // System Interface

// .USER_CLK (gt1_txusrclk2_i),

// .SYSTEM_RESET (gt1_tx_system_reset_c)

// );

//***********************************************************************//

// //

//------------------------ Frame Checkers -----------------------------//

// //

//***********************************************************************//

// The example design uses Block RAM based frame checkers to verify incoming

// data. By default the frame generators are loaded with a data sequence that

// matches the outgoing sequence of the frame generators for the TX ports.

// You can modify the expected data sequence by changing the INIT values of the frame

// checkers in this file. Pay careful attention to bit order and the spacing

// of your control and alignment characters.

// When the frame checker receives data, it attempts to synchronise to the

// incoming pattern by looking for the first sequence in the pattern. Once it

// finds the first sequence, it increments through the sequence, and indicates an

// error whenever the next value received does not match the expected value.

// assign gt0_frame_check_reset_i = (EXAMPLE_CONFIG_INDEPENDENT_LANES==0)?reset_on_data_error_i:gt0_matchn_i;

// gt0_frame_check0 is always connected to the lane with the start of char

// and this lane starts off the data checking on all the other lanes. The INC_IN port is tied off

// assign gt0_inc_in_i = 1'b0;

// gtx_aurora_x2_GT_FRAME_CHECK #

// (

// .RX_DATA_WIDTH ( 32 ),

// .RXCTRL_WIDTH ( 4 ),

// .COMMA_DOUBLE ( 16'h04bc ),

// .WORDS_IN_BRAM(EXAMPLE_WORDS_IN_BRAM),

// .START_OF_PACKET_CHAR ( 32'h060504bc )

// )

// gt0_frame_check

// (

// // GT Interface

// .RX_DATA_IN (gt0_rxdata_i),

// .RXCTRL_IN (gt0_rxcharisk_i),

// .RXENMCOMMADET_OUT (gt0_rxmcommaalignen_i),

// .RXENPCOMMADET_OUT (gt0_rxpcommaalignen_i),

// .RX_ENCHAN_SYNC_OUT ( ),

// .RX_CHANBOND_SEQ_IN (tied_to_ground_i),

// // Control Interface

// .INC_IN (gt0_inc_in_i),

// .INC_OUT (gt0_inc_out_i),

// .PATTERN_MATCHB_OUT (gt0_matchn_i),

// .RESET_ON_ERROR_IN (gt0_frame_check_reset_i),

// // System Interface

// .USER_CLK (gt0_rxusrclk2_i),

// .SYSTEM_RESET (gt0_rx_system_reset_c),

// .ERROR_COUNT_OUT (gt0_error_count_i),

// .TRACK_DATA_OUT (gt0_track_data_i)

// );

// assign gt1_frame_check_reset_i = (EXAMPLE_CONFIG_INDEPENDENT_LANES==0)?reset_on_data_error_i:gt1_matchn_i;

// in the "independent lanes" configuration, each of the lanes looks for the unique start char and

// in this case, the INC_IN port is tied off.

// Else, the data checking is triggered by the "master" lane

// assign gt1_inc_in_i = (EXAMPLE_CONFIG_INDEPENDENT_LANES==0)?gt0_inc_out_i:1'b0;

// gtx_aurora_x2_GT_FRAME_CHECK #

// (

// .RX_DATA_WIDTH ( 32 ),

// .RXCTRL_WIDTH ( 4 ),

// .COMMA_DOUBLE ( 16'h04bc ),

// .WORDS_IN_BRAM(EXAMPLE_WORDS_IN_BRAM),

// .START_OF_PACKET_CHAR ( 32'h060504bc )

// )

// gt1_frame_check

// (

// // GT Interface

// .RX_DATA_IN (gt1_rxdata_i),

// .RXCTRL_IN (gt1_rxcharisk_i),

// .RXENMCOMMADET_OUT (gt1_rxmcommaalignen_i),

// .RXENPCOMMADET_OUT (gt1_rxpcommaalignen_i),

// .RX_ENCHAN_SYNC_OUT ( ),

// .RX_CHANBOND_SEQ_IN (tied_to_ground_i),

// // Control Interface

// .INC_IN (gt1_inc_in_i),

// .INC_OUT (gt1_inc_out_i),

// .PATTERN_MATCHB_OUT (gt1_matchn_i),

// .RESET_ON_ERROR_IN (gt1_frame_check_reset_i),

// // System Interface

// .USER_CLK (gt1_rxusrclk2_i),

// .SYSTEM_RESET (gt1_rx_system_reset_c),

// .ERROR_COUNT_OUT (gt1_error_count_i),

// .TRACK_DATA_OUT (gt1_track_data_i)

// );

// assign TRACK_DATA_OUT = track_data_out_i;

// assign track_data_out_i =

// gt0_track_data_i &

// gt1_track_data_i ;

//-------------------------------------------------------------------------------------

//-------------------------Debug Signals assignment--------------------

assign gt0_rxlpmen_i = tied_to_vcc_i;

assign gt1_rxlpmen_i = tied_to_vcc_i;

//------------ optional Ports assignments --------------

assign gt0_rxprbscntreset_i = tied_to_ground_i;

assign gt0_rxprbssel_i = 0;

assign gt0_loopback_i = 0;

assign gt0_txdiffctrl_i = 0;

assign gt0_rxbufreset_i = tied_to_ground_i;

assign gt0_rxcdrhold_i = tied_to_ground_i;

//------GTH/GTP

assign gt0_rxdfelpmreset_i = tied_to_ground_i;

assign gt0_rxpmareset_i = tied_to_ground_i;

assign gt0_rxpolarity_i = tied_to_ground_i;

assign gt0_rxpd_i = 0;

assign gt0_txprecursor_i = 0;

assign gt0_txpostcursor_i = 0;

assign gt0_txchardispmode_i = 0;

assign gt0_txchardispval_i = 0;

assign gt0_txpolarity_i = tied_to_ground_i;

assign gt0_txpd_i = 0;

assign gt0_txprbsforceerr_i = tied_to_ground_i;

assign gt0_txprbssel_i = 0;

assign gt1_rxprbscntreset_i = tied_to_ground_i;

assign gt1_rxprbssel_i = 0;

assign gt1_loopback_i = 0;

assign gt1_txdiffctrl_i = 0;

assign gt1_rxbufreset_i = tied_to_ground_i;

assign gt1_rxcdrhold_i = tied_to_ground_i;

//------GTH/GTP

assign gt1_rxdfelpmreset_i = tied_to_ground_i;

assign gt1_rxpmareset_i = tied_to_ground_i;

assign gt1_rxpolarity_i = tied_to_ground_i;

assign gt1_rxpd_i = 0;

assign gt1_txprecursor_i = 0;

assign gt1_txpostcursor_i = 0;

assign gt1_txchardispmode_i = 0;

assign gt1_txchardispval_i = 0;

assign gt1_txpolarity_i = tied_to_ground_i;

assign gt1_txpd_i = 0;

assign gt1_txprbsforceerr_i = tied_to_ground_i;

assign gt1_txprbssel_i = 0;

//------------------------------------------------------

// assign resets for frame_gen modules

assign gt0_tx_system_reset_c = !gt0_txfsmresetdone_r2;

assign gt1_tx_system_reset_c = !gt1_txfsmresetdone_r2;

// assign resets for frame_check modules

assign gt0_rx_system_reset_c = !gt0_rxresetdone_r3;

assign gt1_rx_system_reset_c = !gt1_rxresetdone_r3;

assign gt0_drpaddr_i = 9'd0;

assign gt0_drpdi_i = 16'd0;

assign gt0_drpen_i = 1'b0;

assign gt0_drpwe_i = 1'b0;

assign gt1_drpaddr_i = 9'd0;

assign gt1_drpdi_i = 16'd0;

assign gt1_drpen_i = 1'b0;

assign gt1_drpwe_i = 1'b0;

assign soft_reset_i = tied_to_ground_i;

endmodule

3. 在线调试

调试思路:如果没有多余的板卡,你就用ip核进行回环调试,具体看ug476手册第88页进行配置(广子:上xianyu搜麻酱就烧饼,获取xilinx全系列文档手册),近端pcs和近端pma,如果这样调试通了,那基本没问题了。

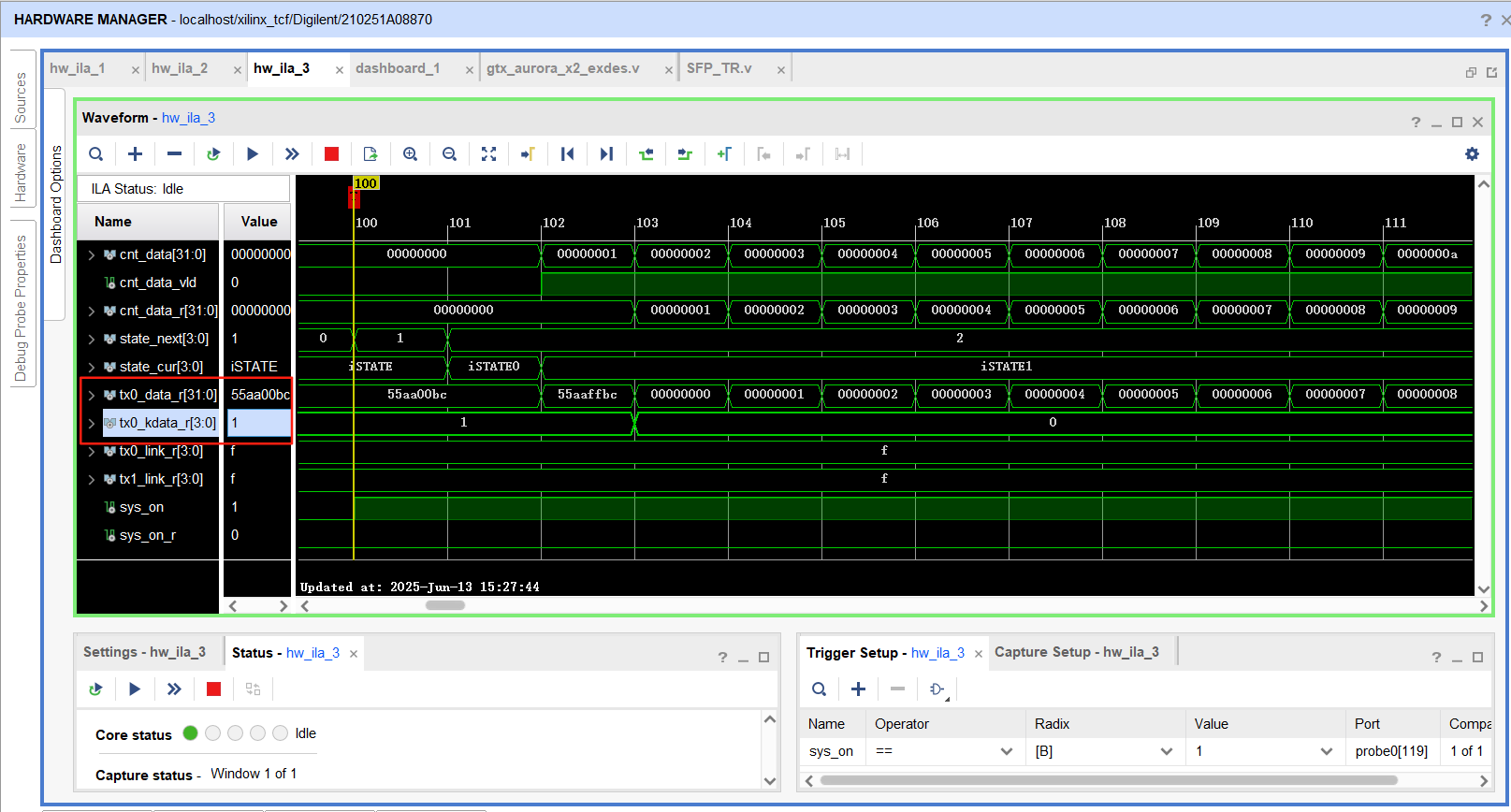

TX链路:

可以很清晰的看到,当我的sys_on拉高的时候,经过编码后的数据包已经有效的发送出去了

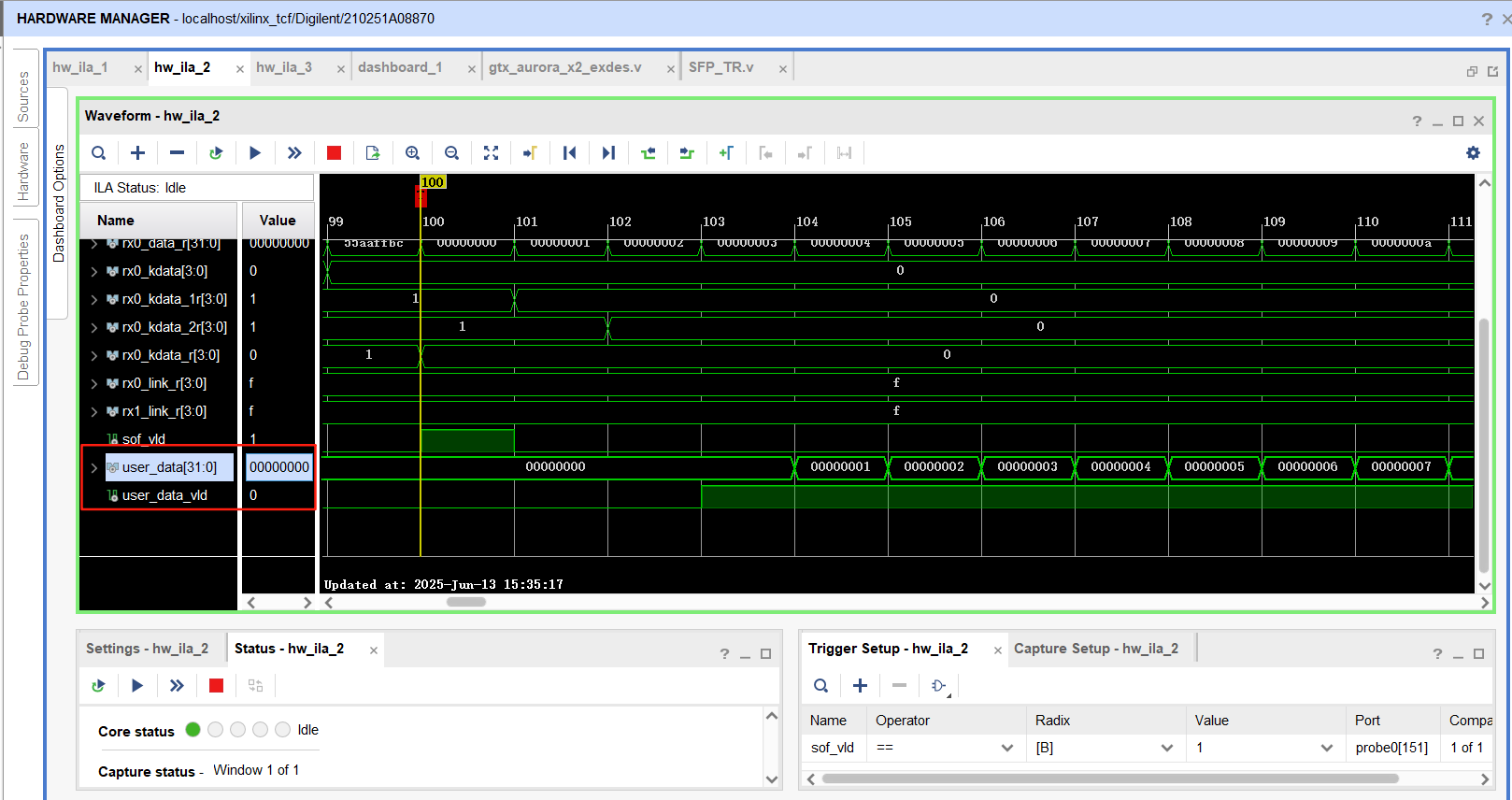

RX链路:

可以看到,当我的vld有效的时候,接收到的正好是发送过来的顺序数,和发送的有效数据包一致!

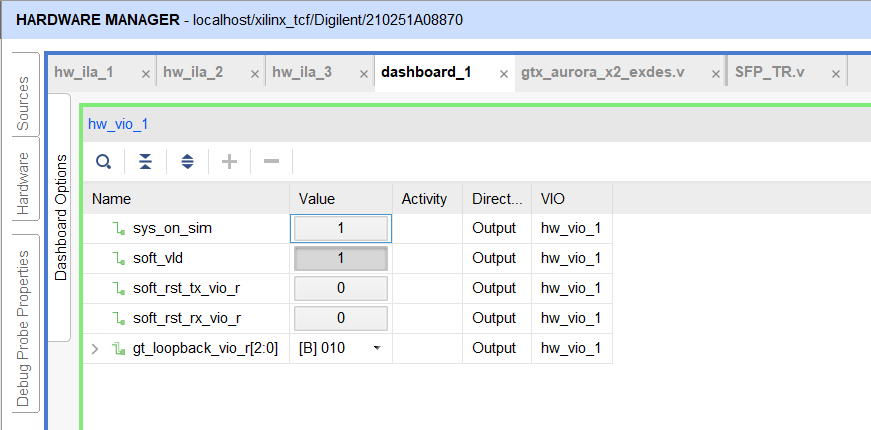

vio调试:

说明:

1.sys_on_sim是总的系统启动信号

2.soft_vld是控制剩余的复位GT链路信号和回环测试的信号

有需要工程源码的同学上xianyu搜麻酱就烧饼找对应源码即可

感谢

创作不易,要是有帮到同学你的地方,我也感到高兴

感谢你能看到最后,好了求个赞赞行吗哈哈哈哈哈哈哈

有问题评论指出,或者你有好点的方法来实现结果,大家一起学习好吗哈哈哈哈哈哈

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)