基于cadence的xcelium和verdi,仿真验证任意FPGA工程

基于cadence的xcelium和verdi仿真验证FPGA工程。

一、FPGA工程建立

使用vivado创建自己的工程如fpga_top,以及包括所有全功能的子模块。将用到的IP例化加入。

二、FPGA仿真lib产生

网上百度,注意的是用linux版本的产生xcelium的lib,win 版本不行,只能产生modelsim的。

三、linux环境搭建

基本的Linux操作,gvim,makefile脚本。

四、cadence工具安装

安装cadence的xcelium和verid软件,或者网上百度下载使用安装好的虚拟机。

五、仿真工程建立

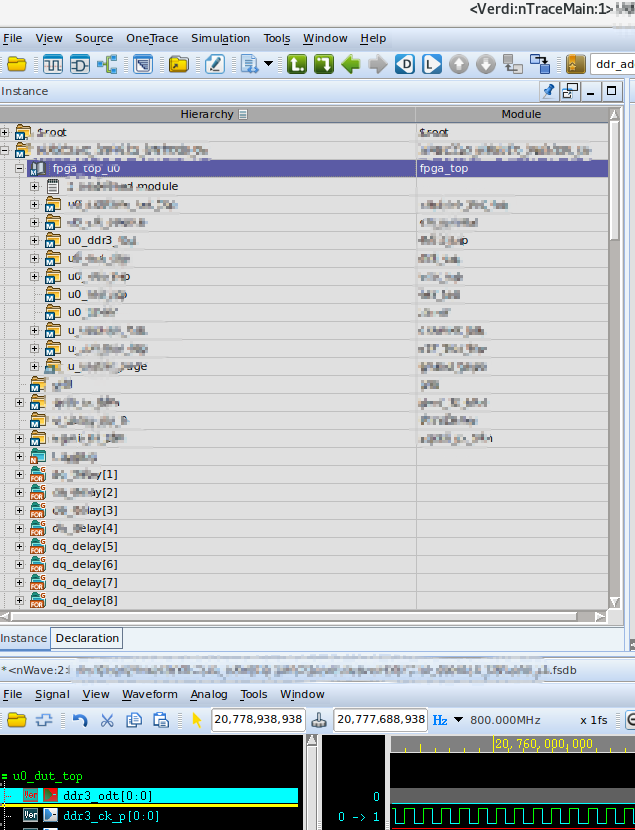

创建sim文件夹用于仿真环境,创建filelist,makefile,仿真tb承载fpga_top,添加仿真激励,包括时钟,复位,仿真model,如有ddr3,可加入用mig产生例子工程,xilinx提供有ddr仿真模型。

tb中用fsdb产生波形文件,如需要matlab也可调用matlab。如仿真网络报文,可加入吃Wireshark产生的 pacp的仿真文件。使用gmii或rgmii。

涉及到的吃xilinx的ip,ip产生的时候有*.gen文件夹,里面有sim_netlist.v,加入filelist,还需加入之前产生的xcelium的lib的cds.lib(工具自动吃,放入sim文件夹即可)

六、仿真运行

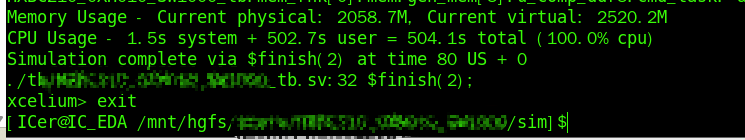

make xrun,加入仿真

make verdi,查看波形

完善中。。。。。。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)