fpga学习_FPGA调用ip核实现ROM_2025_06_5(day 8)

摘要: FPGA存储器实现的关键应用场景包括:1)用ROM存储固定初始值(如芯片寄存器初始化);2)FIFO缓冲高速ADC数据(速率1us/数据,串口输出);3)可修改的RAM(如DDS信号发生器的1024个循环数据)。Vivado开发时需注意:分布式ROM(查找表)和块ROM(硬件RAM)的选择,通过官方文档学习IP核用法。存储器IP配置要点包含端口启用状态、初始化文件加载(可用mif精灵工具)

一、FPGA实现存储器的实际应用场景

1、某芯片、内部有500个寄存器,需要在上电的时候,由fpga向寄存器中写入初始值,初始值已经通过相应的文档给出了具体值,这些值都是已知的。

(1)数据量比较多

(2)数据量已知

ROM(read only memory)(CMOS初始化)

2、信号源(例如ADC)以1us一个的速率产生12位的数据,现要求获得连续1ms内的数据,通过串口以115200的波特率发到电脑。数据量是1000个。

(1)数据量是1000个

(2)数据内容是未知

(3)一秒钟发11520个字节的数据。每个数据发送需要86.8us。

数据生产速率是0.5us一个字节。

(4)数据的生产和消耗时候的位宽不一样。

FIFO(first in first out)(高速数据发送系统)

3、某芯片,一次完整的输出需要1024个14位数据,该芯片开始工作后会循环持续的输出这1024个数据,用户能通过串口来改变这1024个数据的内容。

(1)数据要求能被更改。

(2)数据要能重复使用。

RAM(random access memory)(DDS信号发生器)

4、信号源(例如ADC)以1ms,一个的速率产生12位的数据,现要求获得连续1s内的数据,通过某通信接口以100MB/S的发送到电脑,该通信接口一次发送至少需要连续的512个字节的数据。数据速率不匹配数据消耗速率快于数据生产速率,数据消耗时候要求是连续的。

(1)使用一个通道,数据生产满512个字节之后,再让数据消耗模块开始一次发送。

总线形式、通过以太网或者USB传输数据的应用

二、Vivado中存储器IP的应用

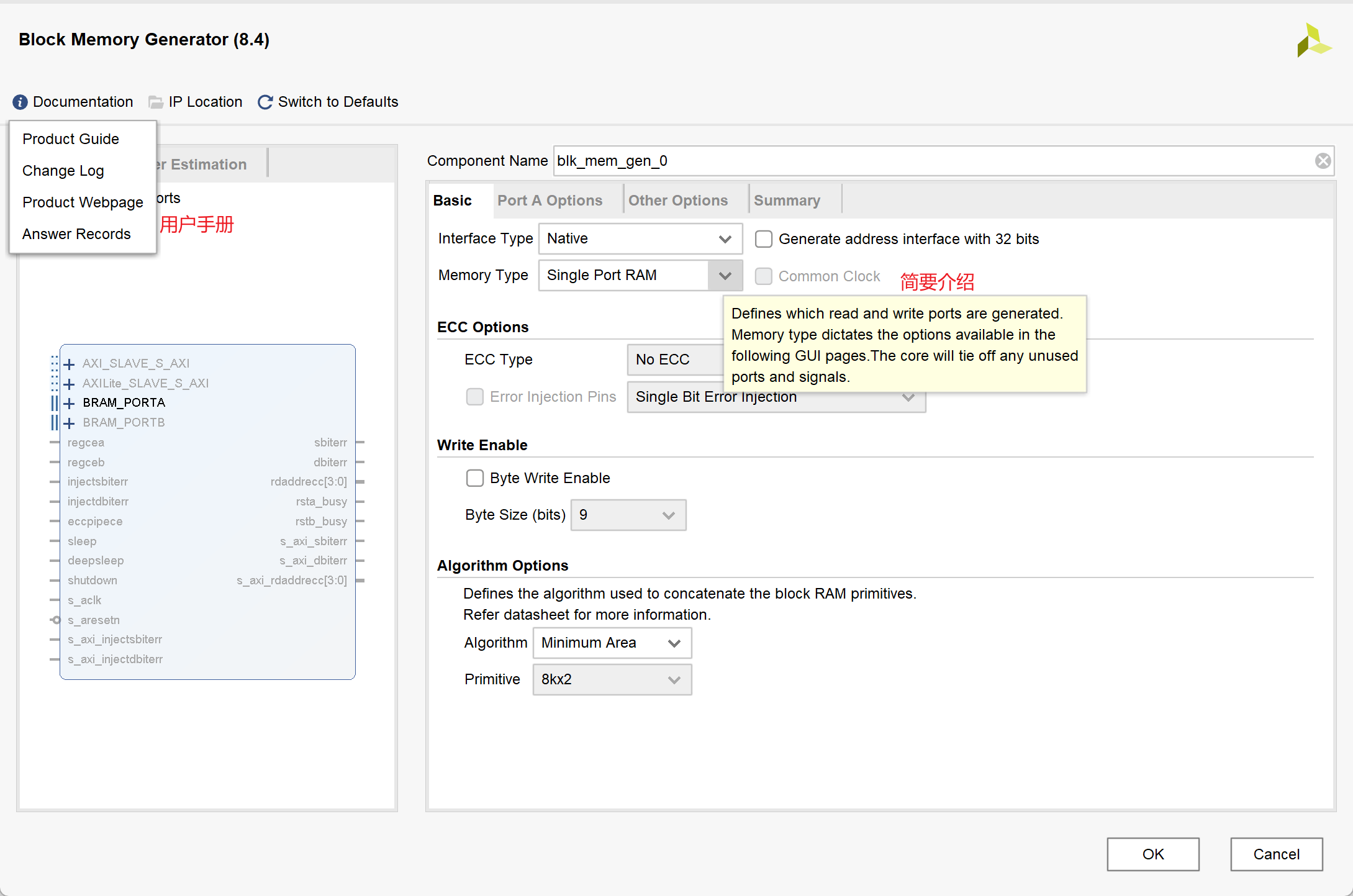

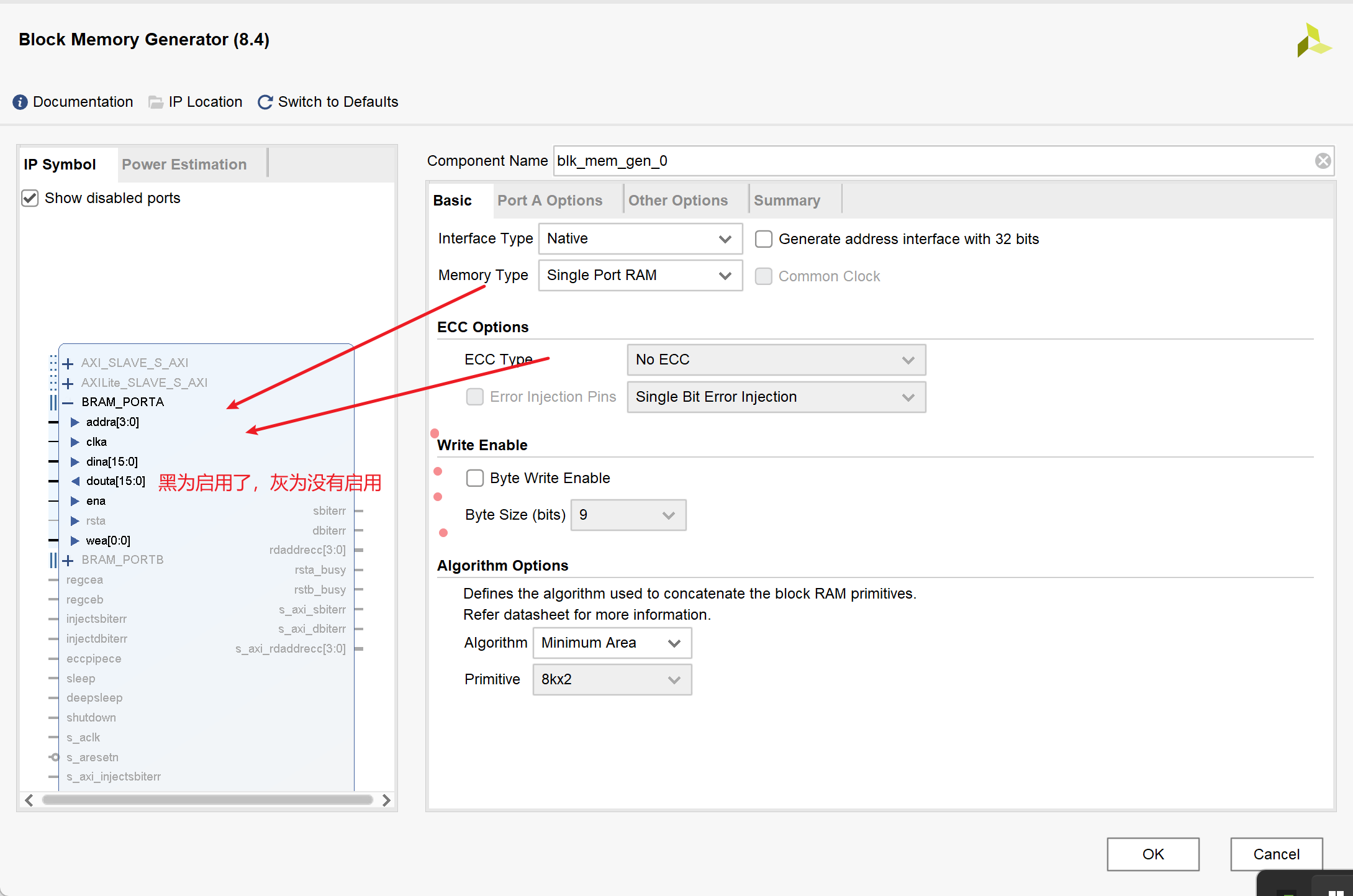

学习方法:阅读手册\对照着IP调用界面旁边的模块看

1、ROM/RAM模块的打开

distributed memory generator分布式ROM(查找表、小型RAM)\block memory generator块ROM(嵌入式硬件RAM)

(1)鼠标停留在栏上可以看到该项的简介

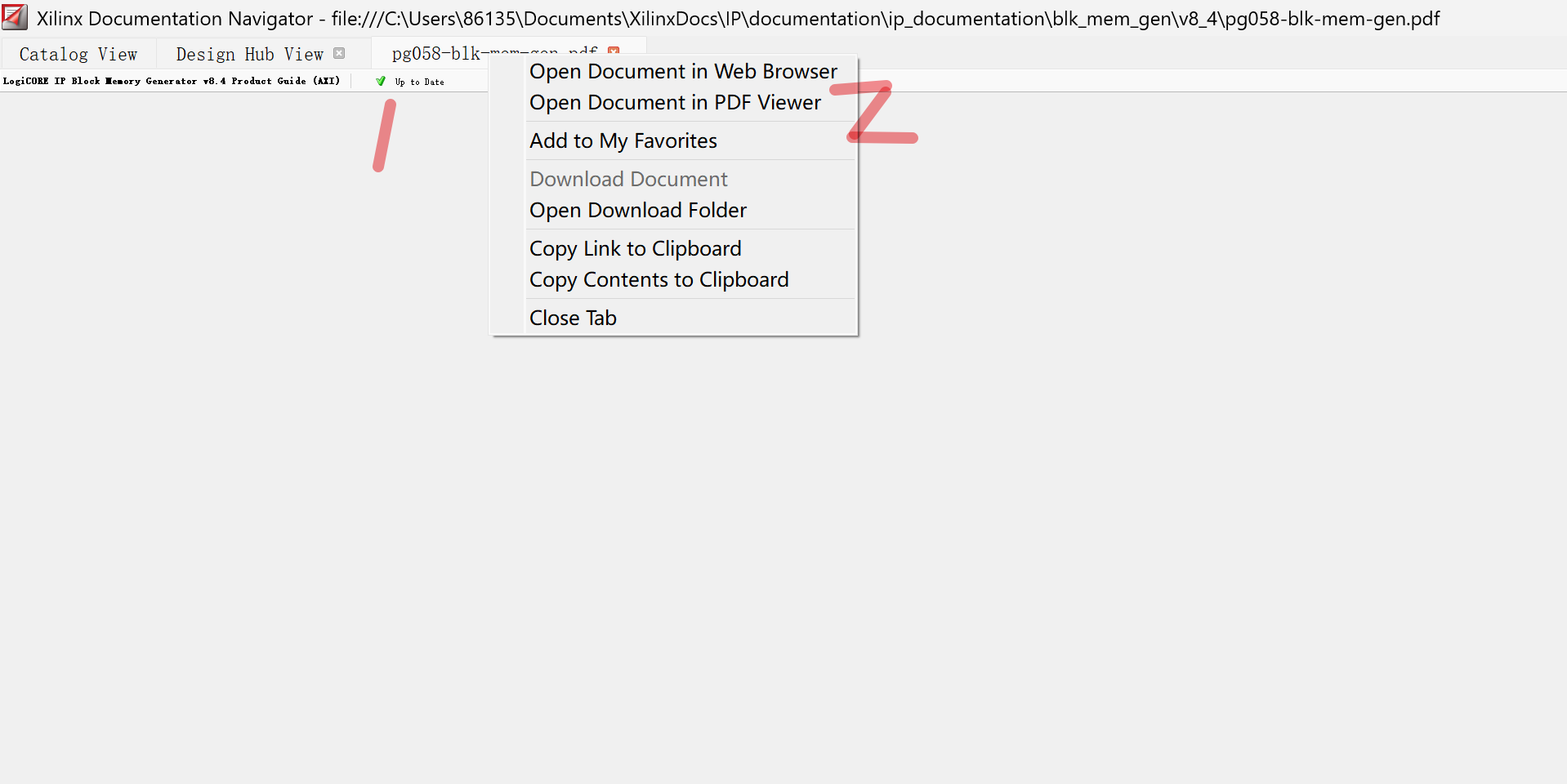

(2)用pdf阅读器读

打不开去官网搜:

https://zhuanlan.zhihu.com/p/545872080

2、模块的调用

(1)修改右边的值,左边的端口会变黑或灰,黑为启用,灰为未启用。

(2)初始化信息

1.加载文件进行初始化(用小梅哥mif精灵)

【原创】Mif精灵/mif(coe)文件生成器 - 芯路恒资料与技术支持专区 - 芯路恒电子技术论坛 - Powered by Discuz!

2.Edit输入(用matlab进行加载)

3、模块展示

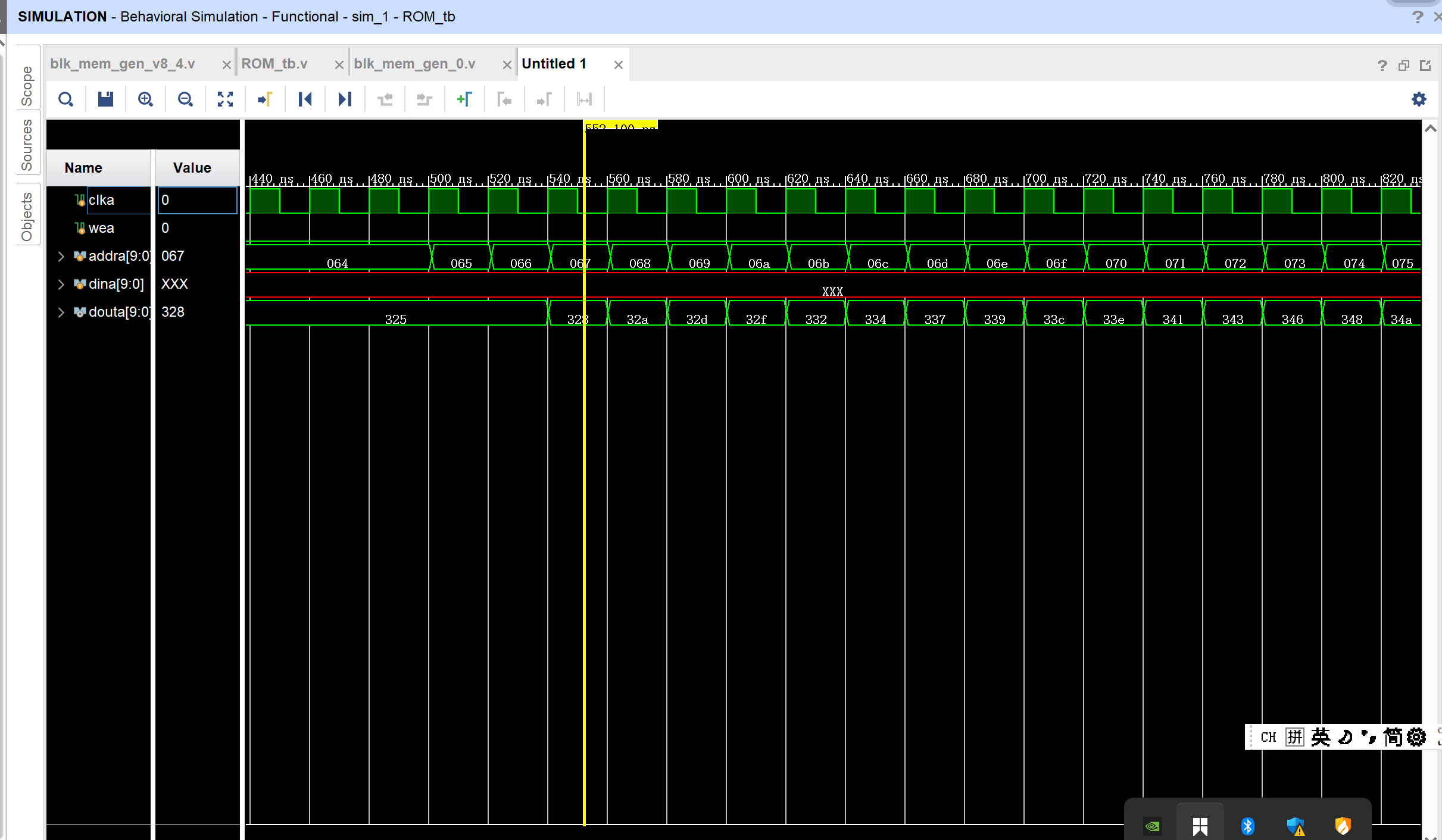

(1)时钟延迟时间可以在ip调用模块中summary看。

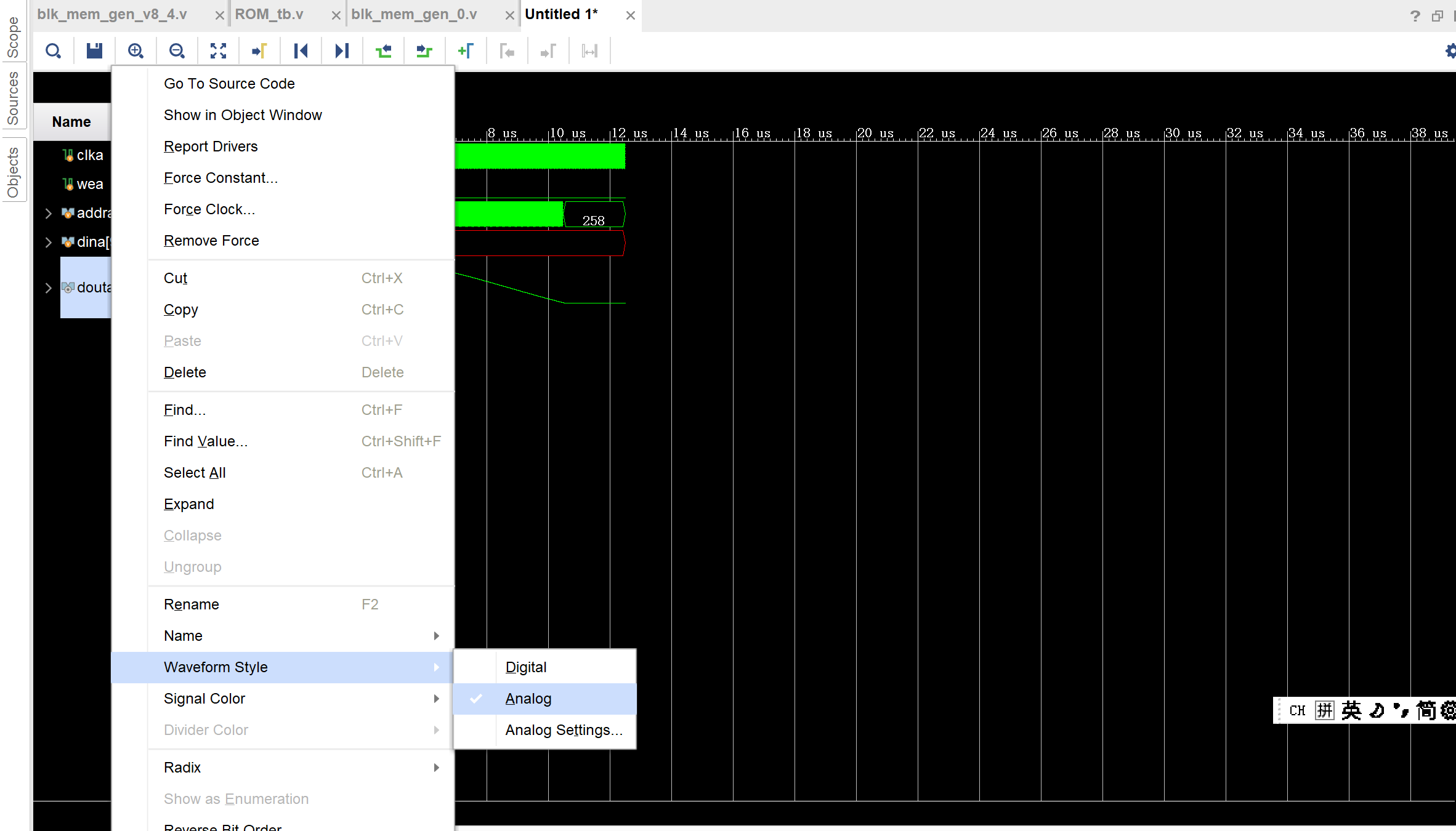

(2)观察模拟数据(可以愉快地做数字信号处理了)

三、代码tb

`timescale 1ns / 1ps

module ROM_tb;

reg clka;

reg wea;

reg [9:0] addra;

reg [9:0] dina;

wire [9:0] douta;

blk_mem_gen_0 rom(

clka,

wea,

addra,

dina,

douta

);

initial clka = 1;

always #10 clka = ~clka;

initial begin

addra = 100;

wea = 0;

#501

repeat(500)begin

addra = addra + 1;

#20; //一个clk

end

#2000

$stop;

end

endmodule

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)