Xilinx XC7A35T开发平台:基于Carry4进位链高精度TDC代码,分辨率71.4p...

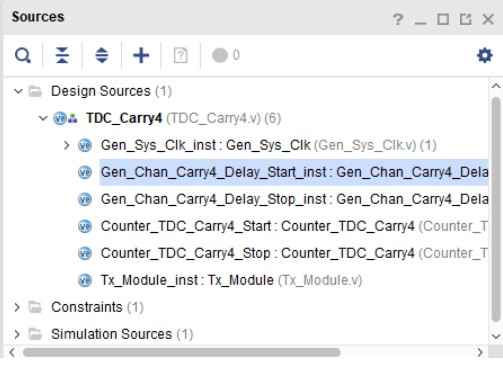

本项目基于Xilinx XC7A35T FPGA开发平台,采用Carry4进位链技术实现高精度时间数字转换(TDC)功能,分辨率可达71.4ps,主要应用于TOF(飞行时间)测距场景。项目代码总数达67个,涵盖时钟管理、TDC核心运算、数据处理与传输等多个模块,通过Verilog和VHDL混合编程,结合Vivado 2017.4开发环境完成综合、实现与仿真验证,最终实现对时间间隔的高精度量化与输出

xilinx xc7a35t 开发平台,基于Carry4进位链高精度时间数字转换(TDC)代码,分辨率71.4ps#tof测距

一、项目概述

本项目基于Xilinx XC7A35T FPGA开发平台,采用Carry4进位链技术实现高精度时间数字转换(TDC)功能,分辨率可达71.4ps,主要应用于TOF(飞行时间)测距场景。项目代码总数达67个,涵盖时钟管理、TDC核心运算、数据处理与传输等多个模块,通过Verilog和VHDL混合编程,结合Vivado 2017.4开发环境完成综合、实现与仿真验证,最终实现对时间间隔的高精度量化与输出。

二、核心模块功能解析

(一)时钟管理模块(clk_wiz_0)

时钟管理模块是整个TDC系统的时序基础,基于Xilinx MMCME2_ADV(高级混合模式时钟管理器)IP核实现,负责将输入时钟进行分频、倍频处理,生成稳定、高精度的系统工作时钟,同时提供时钟锁定状态指示。

1. 关键参数配置

不同版本的clkwiz0模块通过调整MMCME2_ADV的核心参数,适配不同的时钟需求,核心参数配置如下表所示:

| 参数名称 | 配置值(版本1) | 配置值(版本2) | 配置值(版本3) | 配置值(版本4) | 说明 |

|---|---|---|---|---|---|

| CLKIN1_PERIOD | 20.000000ns | 20.000000ns | 20.000000ns | 20.000000ns | 输入时钟周期,对应输入频率50MHz |

| CLKFBOUTMULTF | 26.500000 | 26.000000 | 21.000000 | 21.000000 | 反馈时钟倍频系数 |

| CLKOUT0DIVIDEF | 6.250000 | 6.250000 | 5.000000 | 3.750000 | 输出时钟0分频系数 |

| CLKOUT0DUTYCYCLE | 0.500000 | 0.500000 | 0.500000 | 0.500000 | 输出时钟0占空比,固定为50% |

| COMPENSATION | ZHOLD | ZHOLD | ZHOLD | ZHOLD | 时钟补偿模式,采用ZHOLD补偿减少时序偏差 |

根据上述参数可计算输出时钟频率,以版本1为例,输出时钟频率=(输入频率×CLKFBOUTMULTF)/CLKOUT0DIVIDEF=(50MHz×26.5)/6.25=212MHz,其他版本可通过相同公式计算,满足TDC系统对不同时序精度的需求。

2. 模块接口与功能

- 输入接口:

- clk_in1:50MHz外部输入时钟,为整个时钟模块提供原始时钟源;

- reset:复位信号,高电平有效,用于模块初始化时重置内部状态。

- 输出接口:

- clkout1:经过MMCME2ADV处理后的输出时钟,为TDC其他模块提供稳定时序;

- locked:时钟锁定信号,高电平表示时钟模块已稳定工作,低电平表示时钟未锁定,此时输出时钟不可用。

3. 内部核心结构

模块内部由IBUF(输入缓冲)、BUFG(全局时钟缓冲)、MMCME2_ADV组成:

- IBUF(clkin1ibufg):对外部输入时钟clkin1进行缓冲,减少外部噪声干扰,确保输入时钟的稳定性;

- MMCME2ADV(mmcmadv_inst):核心时钟处理单元,通过倍频、分频、相位调整等操作,生成符合需求的时钟信号,并通过反馈机制(CLKFBIN与CLKFBOUT)实现时钟稳定控制;

- BUFG(clkfbuf、clkout1buf):全局时钟缓冲器,将MMCME2_ADV输出的时钟信号驱动到全局时钟网络,保证时钟信号在FPGA内部传输时的低延迟和低 skew,满足全芯片时序一致性要求。

(二)TDC核心运算模块

TDC核心运算模块是实现时间数字转换的核心,基于Carry4进位链技术,通过对时间间隔的量化,将模拟时间信号转换为数字信号,主要包含GenChanCarry4Delay(进位链延迟生成)和CounterTDC_Carry4(计数与相位处理)两个子模块。

1. Gen_Chan_Carry4_Delay(进位链延迟生成模块)

该模块利用FPGA内部Carry4进位链的固有延迟特性,构建延迟链网络,将输入的触发信号(Trig_TDC)通过不同路径的延迟,生成多个具有固定时间间隔的延迟信号,为后续时间量化提供基础。

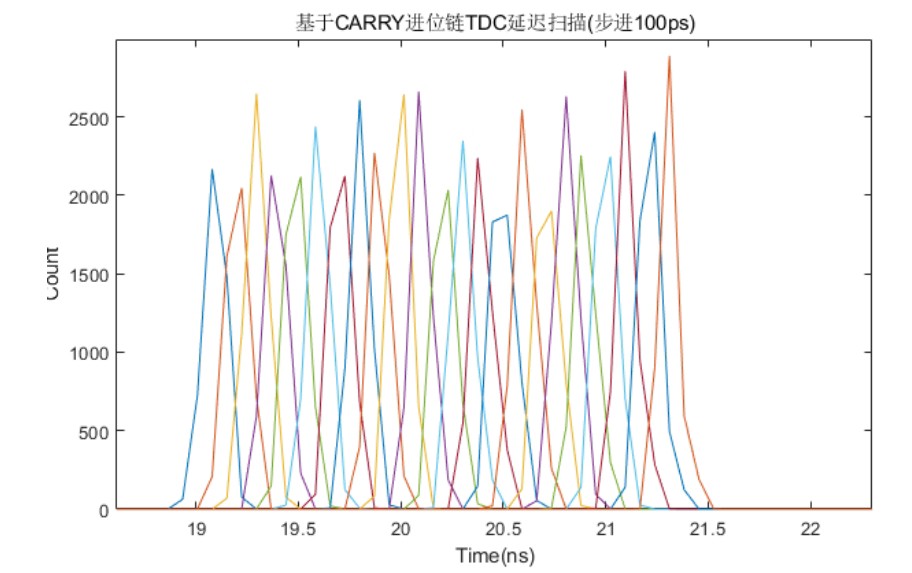

- 工作原理:Carry4进位链是Xilinx FPGA中的专用进位逻辑单元,每个Carry4单元包含4个进位级,每个进位级具有固定的延迟(约71.4ps)。通过级联多个Carry4单元,构建50路延迟链(对应TrigTDC1~TrigTDC50输入),使输入触发信号经过不同延迟后输出,形成时间上依次错开的触发信号序列。

- 关键功能:保证每路延迟信号的延迟时间精准可控,且延迟间隔均匀,为后续CounterTDCCarry4模块捕捉时间相位提供准确的时间基准。

2. Counter_TDC_Carry4(计数与相位处理模块)

该模块是TDC核心运算的关键,负责对GenChanCarry4_Delay输出的延迟触发信号进行采样、计数与相位计算,最终输出量化后的时间数字结果。

(1)模块接口

- 输入接口:

- Reset:系统复位信号,高电平有效,初始化模块内部计数器与寄存器;

- SysClk1:来自clkwiz_0模块的稳定时钟(如212MHz),作为采样与计数时序基准;

- TrigTDC1~TrigTDC50:来自GenChanCarry4_Delay的50路延迟触发信号;

- lopt:优化控制信号,用于选择不同的计数优化模式。

- 输出接口:

- Counter_Value[7:0]:8位计数数值,对应时间量化的整数部分,反映触发信号跨越的时钟周期数;

- Phase_Value[5:0]:6位相位数值,对应时间量化的小数部分,通过进位链延迟计算得到,分辨率71.4ps;

- Validflag:数据有效信号,高电平表示CounterValue和Phase_Value输出有效,可被后续模块读取。

(2)核心功能流程

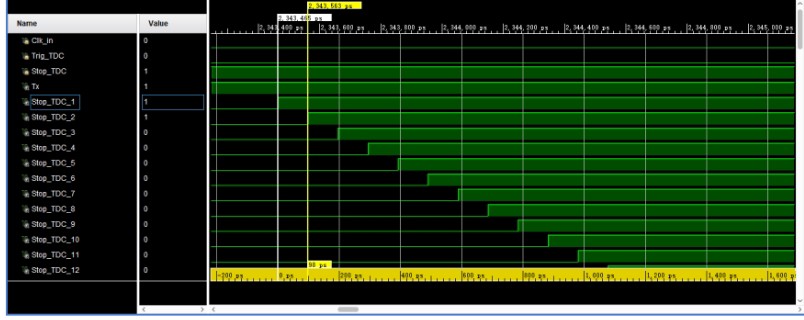

- 信号采样与同步:通过FDRE(带复位的D触发器)对50路TrigTDC信号进行采样(如Signainpose1r~Signainpose50r),将异步触发信号同步到SysClk1时钟域,避免亚稳态问题;

- 数据相位缓存:将采样后的信号存入多级寄存器(DataPhase1、DataPhase1r、DataPhase1r1等),进行相位缓存与稳定,确保后续处理时信号的稳定性;

- 计数与相位计算:

- 计数器(cnt1pose):在SysClk1时钟驱动下,对触发信号的周期数进行计数,生成CounterValue;

- 相位计算:通过LUT(查找表)构建逻辑电路(如PhaseValue[0]i1、PhaseValue[1]i1等),对50路延迟信号的相位差进行计算,结合Carry4进位链的延迟特性,生成Phase_Value,实现71.4ps分辨率的时间量化; - 数据有效判断:通过Phasedone1、Validflagr3regsrl6等信号,判断计数与相位计算是否完成,当数据稳定后,将Validflag置高,指示输出数据有效。

(三)数据传输模块(Tx_Module)

数据传输模块负责将TDC核心运算模块输出的CounterValue和PhaseValue传输到外部设备(如上位机或其他处理单元),实现数据的对外交互,确保量化后的时间数据能够被后续系统利用。

- 核心功能:通过异步串行或并行传输方式,将Valid_flag标记为有效的数据进行格式打包与传输,同时处理传输过程中的时序匹配,避免数据丢失或错位;

- 关键特性:适配不同的传输协议,可根据实际需求调整传输速率,确保数据在传输过程中的完整性和实时性,满足TOF测距等场景对数据实时处理的需求。

(四)系统时钟生成模块(Gen_Sys_Clk)

该模块是clkwiz0模块的辅助模块,负责对clkwiz0输出的时钟进行进一步分发与缓冲,为TDC系统中的GenChanCarry4Delay、CounterTDCCarry4、TxModule等模块提供各自所需的时钟信号,确保每个模块都能获得符合自身时序要求的时钟,同时避免单一时钟故障导致整个系统瘫痪,提高系统可靠性。

三、系统工作流程

- 系统初始化:上电后,reset信号置高,整个TDC系统进入复位状态,clkwiz0模块初始化,开始对输入的50MHz时钟进行处理,当locked信号置高时,时钟模块稳定工作,其他模块开始进入正常工作状态;

- 触发信号输入与延迟生成:外部触发信号(如TOF测距中的发射与接收触发信号)输入到GenChanCarry4Delay模块,经过Carry4进位链延迟网络,生成50路具有固定时间间隔的延迟触发信号(TrigTDC1~TrigTDC_50);

- 时间量化:CounterTDCCarry4模块在SysClk1时钟驱动下,对50路延迟触发信号进行采样、计数与相位计算,生成CounterValue(整数时间)和PhaseValue(小数时间),当数据稳定后,Validflag置高;

- 数据传输:TxModule模块检测到Validflag高电平后,读取CounterValue和PhaseValue,进行数据格式处理后传输到外部设备;

- 循环工作:在Reset信号未置高的情况下,系统重复步骤2~4,持续对输入的触发信号进行时间量化与数据传输,实现连续的TDC功能。

四、关键技术特点

- 高精度时间量化:基于Carry4进位链技术,利用其固定的延迟特性(71.4ps/级),实现高分辨率的时间数字转换,满足TOF测距等对时间精度要求极高的场景;

- 稳定的时钟系统:采用MMCME2_ADV高级时钟管理器,结合全局时钟缓冲(BUFG),确保时钟信号的低延迟、低 skew,为整个系统提供稳定的时序基础,减少时序偏差对TDC精度的影响;

- 高可靠性设计:通过多级寄存器同步、数据缓存、复位控制等机制,避免亚稳态、数据丢失等问题,同时时钟模块的locked信号为系统提供时钟状态判断,提高系统工作可靠性;

- 灵活的可配置性:clkwiz0模块支持多种参数配置,可根据实际需求调整输出时钟频率,CounterTDCCarry4模块的lopt信号支持不同计数优化模式,适配不同应用场景的需求。

五、设计工具与环境

- 开发工具:Xilinx Vivado 2017.4(win64),用于代码编写、综合、实现、仿真与比特流生成;

- 目标器件:Xilinx XC7A35TFGG484-2 FPGA,该器件具有丰富的Carry4进位链资源和时钟管理资源,满足TDC高精度与高稳定性的需求;

- 仿真工具:支持ActiveHDL、ModelSim、Questa、Riviera、VCS、XSim等多种仿真工具,通过编译脚本(如compile.do)和仿真脚本(如simulate.do)实现功能仿真与时序仿真,验证模块功能正确性与时序性能。

六、总结

本基于XC7A35T的Carry4进位链高精度TDC系统,通过合理的模块划分(时钟管理、核心运算、数据传输),结合FPGA专用硬件资源(Carry4、MMCME2_ADV、BUFG),实现了71.4ps分辨率的时间数字转换功能。系统具有高精度、高稳定性、高可靠性的特点,可广泛应用于TOF测距、激光雷达、高精度时序测量等领域。后续可根据实际需求,进一步优化时钟参数、扩展延迟链长度或增加数据处理算法,提升系统性能与适用范围。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)