Zynq开发实践(FPGA之组合逻辑、时序逻辑)

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】 整个数字电路里面,最重要的就是组合逻辑和时序逻辑。有了这两部分做基础,就可以做其他部分的功能了。学习数字电路的时候,主要介绍的内容也就是怎么用组合逻辑芯片、触发器芯片来构建基本数字电路。现在有了verilog之后,就不再需要我们真的去搭建数字电路,只需要我们用verilog去描述对

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

整个数字电路里面,最重要的就是组合逻辑和时序逻辑。有了这两部分做基础,就可以做其他部分的功能了。学习数字电路的时候,主要介绍的内容也就是怎么用组合逻辑芯片、触发器芯片来构建基本数字电路。现在有了verilog之后,就不再需要我们真的去搭建数字电路,只需要我们用verilog去描述对应的数字电路就可以了。剩下来的工作完全可以通过quartus或者是vivado去完成即可。

1、verilog只有一小部分可以综合

verilog的语法其实是很多的,但是从可综合性来说,一般分成两种,即可综合电路、不可综合电路。并且,不可综合电路的语法要比可综合电路的语法多很多。我们记忆的时候,原则上了解module、input、output、assign、wire、reg、if、else、case、always、posedge等可综合语法就好了,剩下来的都是不可以综合的。

那么既然很多的语法都是不可综合的,不可以转换成网表下载到fpga上面的,为什么还要存在呢。答案就是一个,那就是为了仿真测试。比如while和for这种语法,没有一丝可综合的可能性,但是测试用起来很方便。

2、组合逻辑是基础

所谓的组合逻辑,就是基本的与、或、非、异或四个部分。其他的功能,都可以在这四个部分基础之上,组合而成。组合逻辑本身就是一个直肠子,有什么输入,就会有什么输出,这是组合逻辑最大的一个特点。

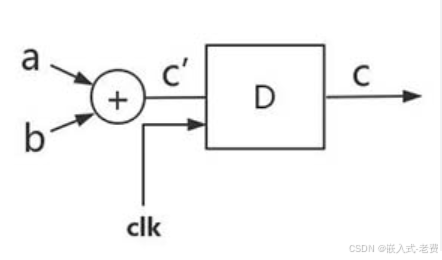

3、时序逻辑是根本

如果数字电路只有组合逻辑,没有时序逻辑,其实意义不大的。时序逻辑,第一次让电路有了记忆属性。整个电路起作用,只有在clk上升沿发生的时候,才会发生信号翻转,其他的时间都是信号不变,维持记忆功能。就是这个记忆功能,让数字电路有了一个质的飞跃。

有了记忆,就可以自由设定计数器;有了记忆,我们就可以设计各种各样的状态机;有了记忆,各种各样的协议都可以借助它来实现。这就是时序逻辑的意义。这个时候,器件的输出,不仅仅和输入有关,还和当前的状态有关,这就很有意义了。

以一个自动贩卖机为例,假设饮料的价格是3元,等到3个硬币都投入之后,这个时候才会吐出商品。所以看上去客户是一个、一个投入硬币,但是每次投入硬币之后,当前的系统状态就会发生改变,直到第三个硬币输入的时候,才会售出商品。当然,如果中途出现反悔也是可以的,一种简单的做法就是在一个、一个吐出硬币,修改当前的系统状态。

还有一个范例就是算法加速。实际开发加速ip的时候,算法部分都是算法工程师先设计好的,一般都是c语言。这个时候数字工程师拿到算法,拆解成数字ip。为了性能的需要,一般时钟和时钟之间的组合逻辑,都尽可能短。这就导致一个算法,需要很多个clock才能完成。试想一下,如果没有时序逻辑作为基础,其实算法转verilog加速是根本没有办法完成的。

4、自上而下设计

数字电路设计的时候,一般都是自上而下设计的。首先是业务功能,其次是中间层,最后才是底层协议。这就要求我们平时开发的时候,就要做好相关代码的整理,比如led、比如按键、比如uart和iic等协议。只有平时积累到足够多的verilog代码基础,才能在真正开发的时候游刃有余。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献10条内容

已为社区贡献10条内容

所有评论(0)