xilinx vivado verilog srio源代码工程,包含维护包、读写和门铃等功能...

SRIO CBB(Common Build Block)可重用模块是基于Xilinx Virtex-5/6 FPGA平台的Serial RapidIO接口解决方案。该模块的核心设计目标是将复杂的SRIOV56 IP核的Local Link接口转换为标准FIFO接口,显著降低SRIO协议的使用难度,使初中级工程师能够快速实现高速串行通信功能。

xilinx vivado verilog srio源代码工程,包含维护包、读写和门铃等功能,顶层封装为fifo,操作简单,简单修改即可应用到实际工程中,附含srio使用说明文档和license

1. 模块概述

SRIO CBB(Common Build Block)可重用模块是基于Xilinx Virtex-5/6 FPGA平台的Serial RapidIO接口解决方案。该模块的核心设计目标是将复杂的SRIOV56 IP核的Local Link接口转换为标准FIFO接口,显著降低SRIO协议的使用难度,使初中级工程师能够快速实现高速串行通信功能。

1.1 设计初衷

- 接口简化:将信号众多的Local Link接口转换为标准FIFO接口

- 协议屏蔽:通过分离控制字和传输数据,简化协议复杂度

- 功能优化:针对高速实时处理系统精简SRIOV56 IP功能,提高应用效率

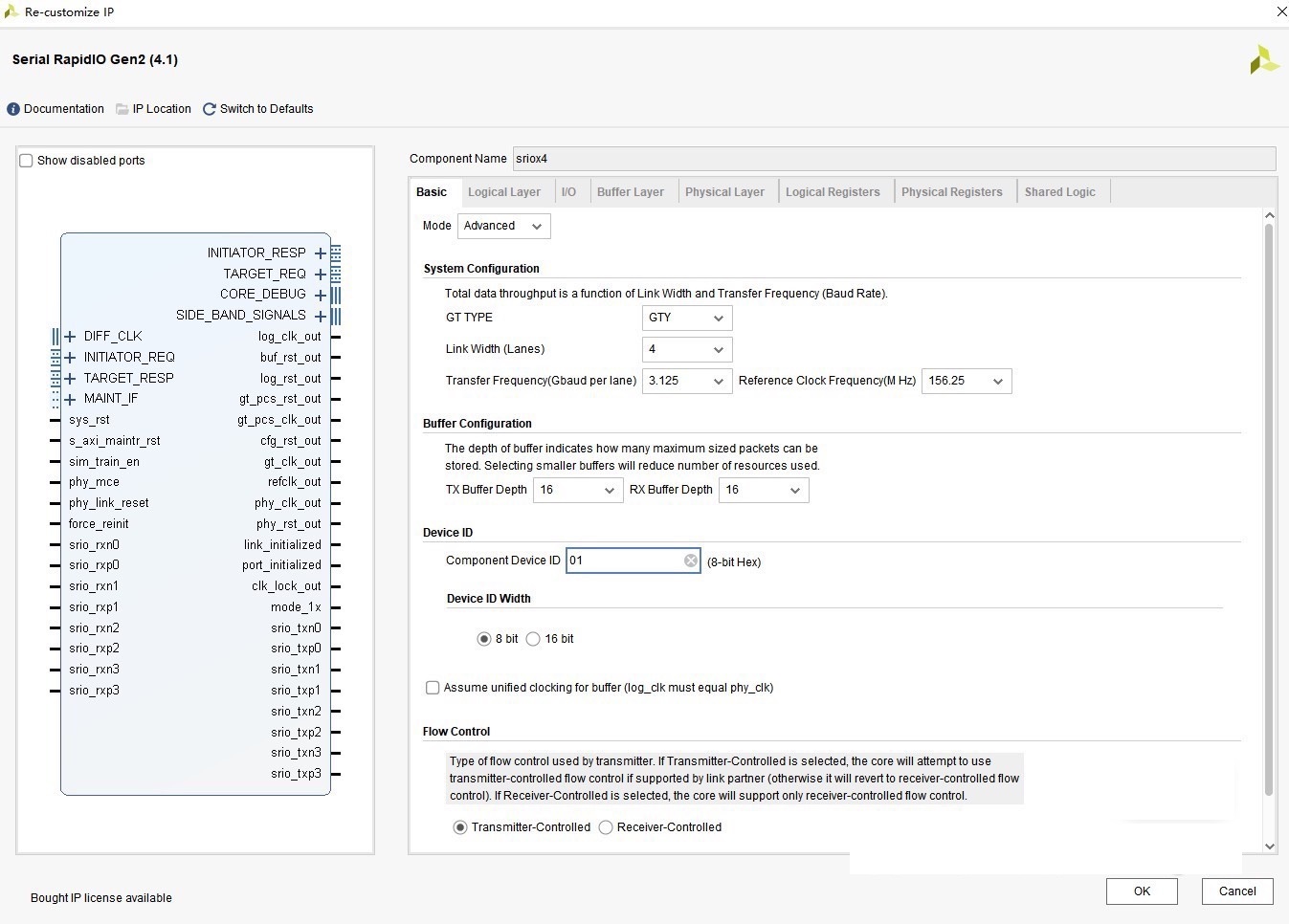

1.2 技术规格

- 开发平台:ISE14.1

- 目标器件:Virtex-5/6 FPGA

- 传输模式:4x位宽,2.5Gbps传输速率

- 参考时钟:125MHz GTP参考时钟

- 硬件描述语言:Verilog HDL

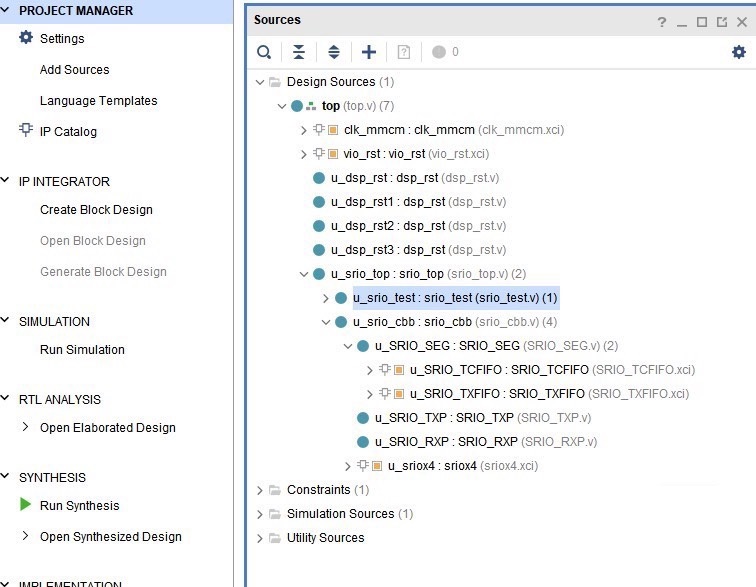

2. 架构设计

2.1 模块组成

SRIO CBB 完整架构

┌─────────────────────────────────────────┐

│ APP LOGIC │

└─────┬─────────────┬─────────────┬───────┘

│ │ │

┌─────▼─────┐ ┌─────▼─────┐ ┌─────▼─────┐

│ TCFIFO │ │ TXFIFO │ │ SETID │

│ (控制字) │ │ (发送数据)│ │ (ID配置) │

└─────┬─────┘ └─────┬─────┘ └─────┬─────┘

│ │ │

┌─────▼─────────────▼─────────────▼─────┐

│ SEG 分片模块 │

└─────────────────┬─────────────────────┘

│

┌─────────────────▼─────────────────────┐

│ TXP 发送模块 │

└─────────────────┬─────────────────────┘

│

┌─────────────────▼─────────────────────┐

│ CORE (SRIO IP核) │

└─────────────────┬─────────────────────┘

│

┌─────────────────▼─────────────────────┐

│ RXP 接收模块 │

└─────────────────┬─────────────────────┘

│

┌─────┬───────────┼───────────┬─────────┐

│ │ │ │ │

┌─▼─┐ ┌─▼─┐ ┌─▼─┐ ┌─▼─┐ ┌─▼─┐

│DB │ │RX │ │状态│ │ID │ │时钟│

│FIFO│ │FIFO│ │寄存│ │输出│ │复位│

└───┘ └───┘ └───┘ └───┘ └───┘2.2 核心模块功能

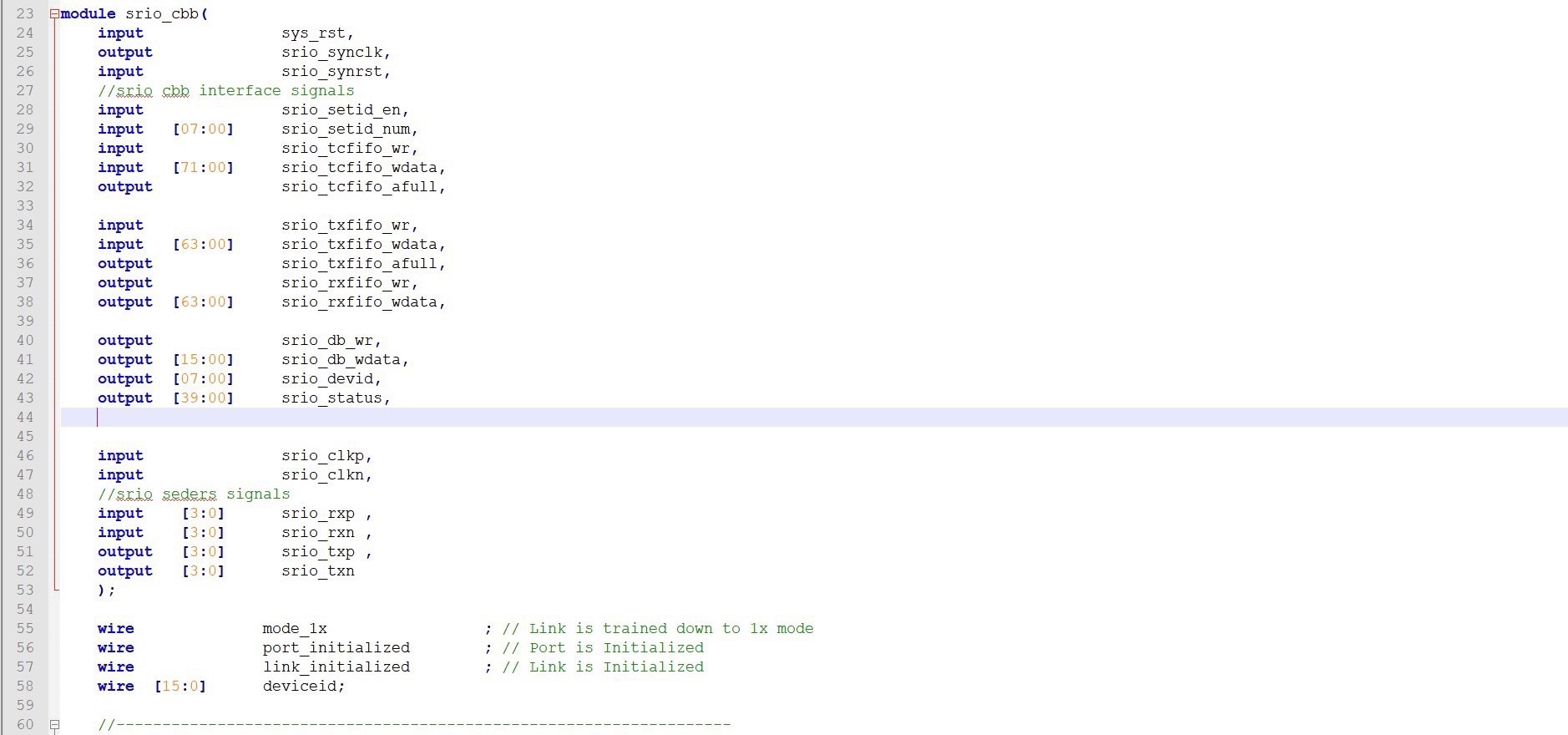

CLK_RST 时钟复位模块

- sriov56_clk:通过MMCM产生CORE和工作时钟

- rio_reset:通过FSM控制RapidIO复位序列的发送和接收

CORE RapidIO顶层封装

- 集成Physical Layer core、Logical Layer core

- 包含Buffer design、RegisterManager reference design

- 实现完整的Serial RapidIO总线协议规范

SEG 分片模块

- 将大于256字节的数据包自动分片传输

- 减少APP逻辑更新控制字的频率

- 提高传输带宽利用率

TXP 发送控制模块

- 将APP逻辑命令转换为CORE识别的Local Link信号

- 协调CORE和APP逻辑两端的有效状态

- 控制总线接口时序

RXP 接收控制模块

- 解析CORE的Local Link接口信号

- 提取控制字信息和传输数据

- 以FIFO接口时序传递给APP逻辑

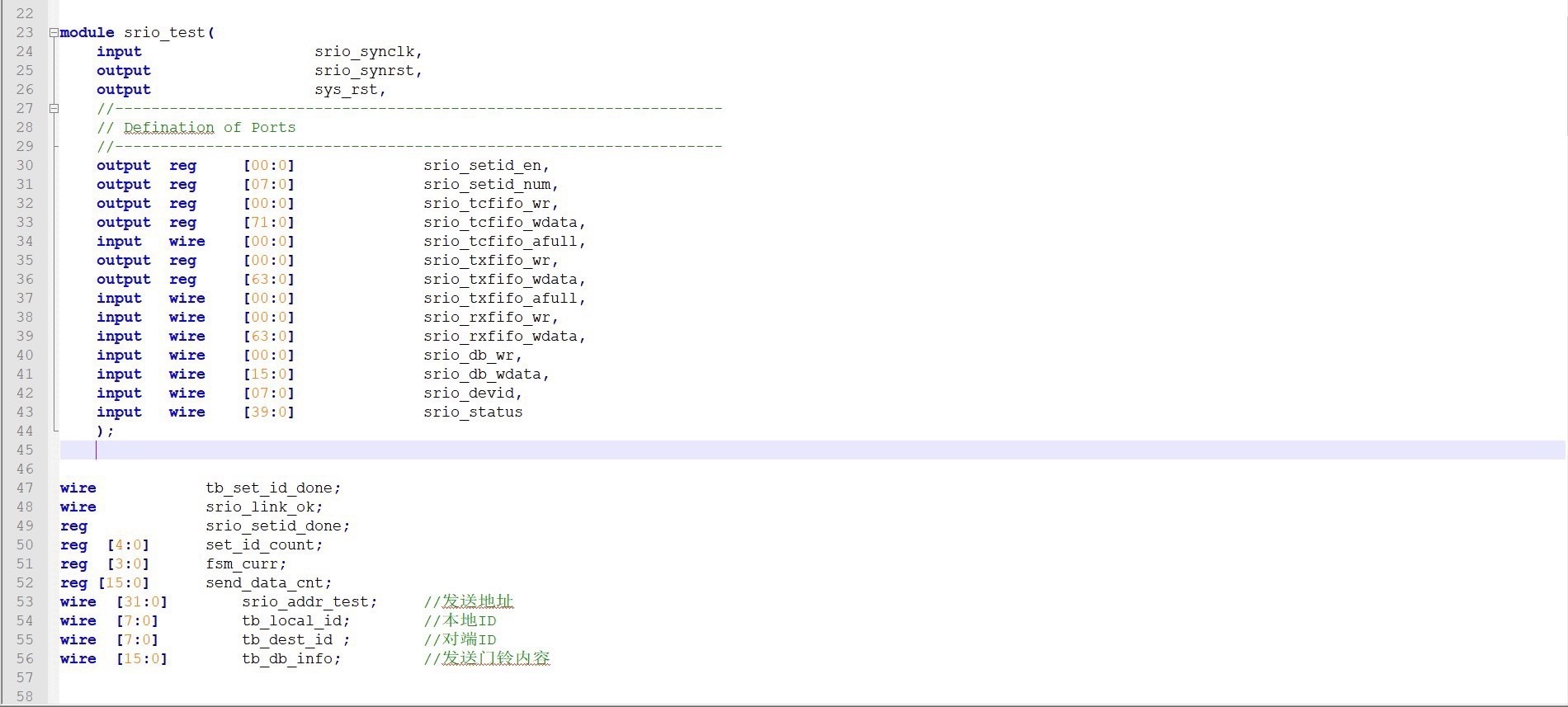

3. 接口信号详解

3.1 关键接口信号

配置接口

sriosetiden:设置本地SRIO ID使能sriosetidnum:8位本地SRIO ID信息

发送接口

sriotcfifowr/wdata:发送控制字FIFO(72位)sriotxfifowr/wdata:发送数据FIFO(64位)sriotcfifoafull/txfifo_afull:FIFO将满状态指示

接收接口

sriodbfifowr/wdata:接收门铃信息(16位)sriorxfifowr/waddr/wdata:接收数据FIFOsriorxfifoafull:接收FIFO将满状态

状态监测

srio_devid:当前SRIO ID输出srio_status:32位状态寄存器,包含链路状态、FIFO状态等

4. 操作模式与数据传输

4.1 配置本地SRIO ID

操作流程:

- 在

user_synclk时钟域下操作 - 置位

sriosetiden使能信号 - 在

sriosetidnum总线上设置目标ID - 等待约16个周期后,

srio_devid更新为新ID

时序特点:ID配置不会立即生效,需要CORE内部寄存器操作完成

4.2 门铃操作

发送门铃

控制字格式:

位域分配:

71:36 保留字 (0x0)

35:28 目标设备ID (dest_id)

27:12 门铃信息 (doorbell_info)

11:8 流控制 (0x1 - 优先级1)

7:0 操作码 (0xA0 - 发送门铃)示例:0x1212345a0表示:

- 目标ID:0x12

- 门铃信息:0x1234

- 传输优先级:1

接收门铃

- 通过

sriodbfifowdata直接获取16位门铃信息 - 操作时钟为

srio_synclk

4.3 数据传输模式

4.3.1 不带响应正常模式 (NWRITE)

控制字格式:

71:68 保留字 (0x0)

67:36 目标地址 (dest_addr)

35:28 目标设备ID (dest_id)

27:12 数据长度 (length,单位DW-64bit)

11:8 流控制 (优先级)

7:0 操作码 (0x54 - NWRITE)传输特点:

- 发送节点无需等待响应即可发送下一个数据块

- 数据传输效率高

- CBB内部自动处理数据分片

4.3.2 带响应正常模式 (NWRITE_R)

控制字格式:与NWRITE相同,但操作码为0x55

传输特点:

- 每个数据块发送后必须等待远端响应

- 传输可靠性更高

- 带宽低于不带响应模式

4.3.3 流模式 (SWRITE)

控制字格式:操作码为0x60

传输特点:

- 只能传输8字节整数倍长度的数据

- 包头格式更简单,有效带宽略高

- 接口时序与正常模式相同

4.4 数据接收处理

接收特性:

- 完整数据包可能被分成多个BLOCK依次接收

- 每个BLOCK的起始地址通过

sriorxfifowaddr指示 - 同一Packet内各BLOCK起始地址递增

5. 关键使用注意事项

5.1 初始化配置

- SRIO ID配置:数据传输前必须配置本地SRIO ID

- 软复位处理:执行SRIO Core软复位后需重新配置SRIO ID

- 链路就绪:必须在

lnk_trdy有效后进行ID配置和数据传输

5.2 接口操作规范

- 分时操作:

sriosetiden、sriotcfifowr、sriotxfifowr必须分时使能 - 操作顺序:必须先写TCFIFO再写TXFIFO

- 长度一致性:TCFIFO中指定的长度必须与实际写入TXFIFO的数据长度一致

- 状态检测:必须检测

*_afull信号,避免FIFO溢出

5.3 错误处理与调试

- 物理链路异常:检查

linktrdy/linkrrdy状态 - 数据丢失:检查FIFO将满信号检测和链路状态

- 传输带宽下降:检查链路状态、模式选择和信号质量

- 门铃传输超时:验证SRIO路由设置和本地ID配置

6. 性能优化建议

6.1 带宽优化

- 优先使用不带响应模式(NWRITE)以获得更高带宽

- 合理设置数据包大小,减少分片开销

- 确保接收端能够及时处理数据,避免反压

6.2 资源利用

- 根据实际需求选择是否例化DBFIFO和RXFIFO

- 合理设置FIFO深度,平衡资源使用和性能

- 利用CBB提供的状态监测功能进行系统调优

7. 应用场景

SRIO CBB模块特别适用于以下场景:

- 高速数据采集系统

- 实时信号处理平台

- 多处理器互联系统

- 雷达、通信等需要高速串行通信的领域

该模块通过简化的FIFO接口和完整的协议处理,为FPGA设计人员提供了高效、可靠的Serial RapidIO通信解决方案,显著降低了高速串行接口的设计复杂度。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)