FPGA学习的必经之路:跑马灯

本教程详细介绍了使用Vivado开发工具实现FPGA跑马灯效果的全过程。以正点原子领航者开发板为例,通过Verilog编程控制PL端LED灯交替闪烁。文章包含工程创建、模块定义、代码编写(含系统时钟计数和复位控制逻辑)、I/O引脚分配以及最终实现步骤。核心代码利用计数器实现0.5秒间隔的LED状态切换,通过系统时钟和复位信号触发控制。完成综合、实现、生成比特流后,最终在硬件上成功实现两个LED灯的

Vivado开发流程:FPGA初步教程实战:点亮LED灯,步骤清晰,必能跟下来

创建工程

正点原子领航者开发板在右下方板载了4颗LED灯,左侧两个位于PL端,右侧两个则位于PS端。本文的目的,是让PL端的LED灯交替点亮并熄灭,从而产生跑马灯的效果。

通过对系统时钟进行计数,可以实现LED灯的亮暗交替。另一方面,为了防止程序在运行时出现异常,可通过复位来将程序恢复至默认状态。因此,程序需要有两个输入,而输出则可通过一个二位宽的向量来表示。因此,在创建Vivado工程是,在弹出的Define Module窗口中,需要

| Port Name | Direction | Bus | MSB | LSB |

|---|---|---|---|---|

| sys_clk | input | 不勾选 | - | - |

| sys_rst | input | 不勾选 | - | - |

| led | output | 勾选 | 1 | 0 |

代码

进入Vivado的默认布局页面后,找到flow_led.v,将其内容更改如下

module flow_led(

input sys_clk,

input sys_rst,

output reg [1:0] led

);

reg [24:0] cnt ; //计数器

//计数器计时0.5s

always @(posedge sys_clk or negedge sys_rst) begin

if(!sys_rst)

cnt <= 25'd0;

else if(cnt < 25'd2499_9999)

cnt <= cnt + 25'd1;

else

cnt <= 25'd0;

end

//对LED灯进行移位控制,以输出2位LED的状态

always @(posedge sys_clk or negedge sys_rst) begin

if(!sys_rst)

led <= 2'b01;

else if(cnt == 25'd2499_9999)

led <= {led[0],led[1]};

else

led <= led;

end

endmodule

其中,【always @】语句用于事件触发,后面的括号里是触发条件,其中posedge是上升沿触发,negedge是下降沿触发。

这两个触发代码块的触发条件是一致的,都是在系统时钟上升沿或者复位信号下降沿时触发。触发后,如果复位信号为0,则将cnt赋值为0,将led赋值为1。如果复位信号不为0,则开始计数,且当cnt刚好等于2499_9999时,调换led[0]和led[1]的值。

实现

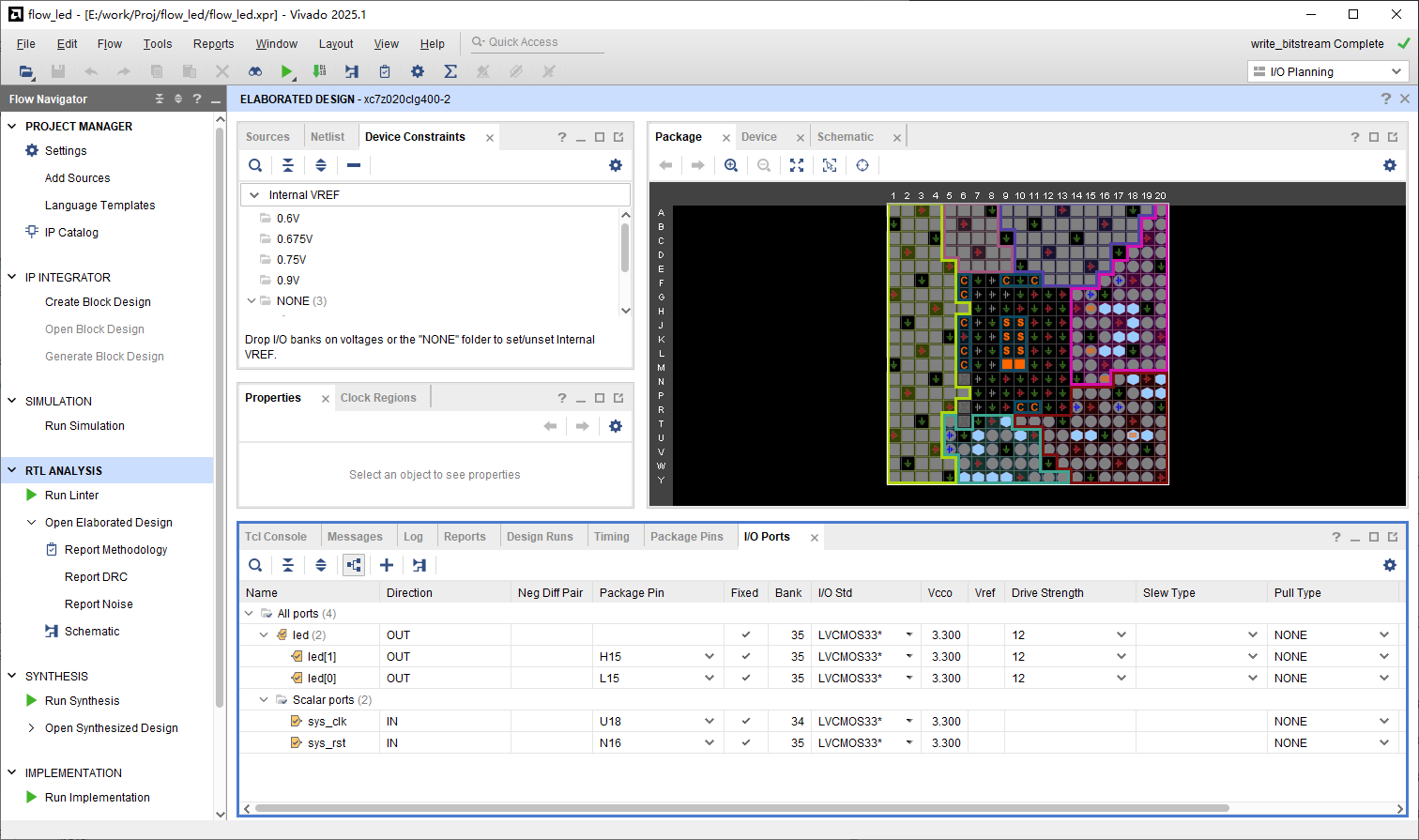

首先【Open Elaborated Design】,分配I/O引脚,引脚名flow_led,引脚参数如下

| Name | Package Pin | I/O Std | 说明 |

|---|---|---|---|

| led[0] | H15 | LVCMOS33 | PL_LED0 |

| led[1] | L15 | LVCMOS33 | PL_LED1 |

| sys_clk | U18 | LVCMOS33 | 系统时钟50MHz |

| sys_rst | N16 | LVCMOS33 | 复位键,低电平有效 |

然后,【Run Synthesis】 -> 【Run Implemented】 -> 【Generate Bitstre】 -> 【Open Hardware Manager】->【Auto Connect】->【Program】。

至此,就可以看到FPGA板子上PL端的两个LED交替闪烁了。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)