ku115上实现adc12dj3200 配置,jesd204b接口,单通道采集模式,204b设...

最近在搞一个项目,需要在KU115上实现ADC12DJ3200的配置,涉及到JESD204B接口,单通道采集模式,204B设置为8lane,6G采样率。我们用的是单通道模式,204B接口设置为8lane,采样率6G。ku115上实现adc12dj3200 配置,jesd204b接口,单通道采集模式,204b设置为8lane,6G采样率,ad和时钟芯片配置代码,完整一套vivado2017.4工程。

ku115上实现adc12dj3200 配置,jesd204b接口,单通道采集模式,204b设置为8lane,6G采样率,ad和时钟芯片配置代码,完整一套vivado2017.4工程

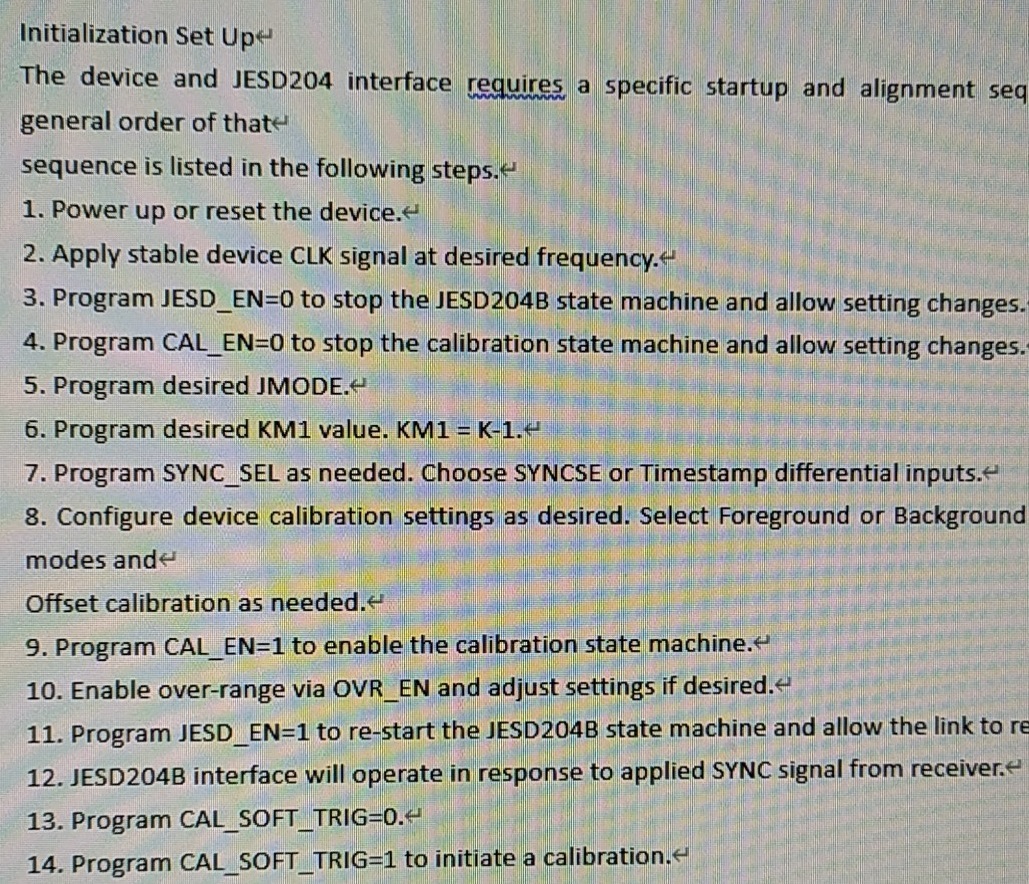

最近在搞一个项目,需要在KU115上实现ADC12DJ3200的配置,涉及到JESD204B接口,单通道采集模式,204B设置为8lane,6G采样率。整个过程有点复杂,但搞定了之后还是挺有成就感的。今天就来分享一下整个配置过程,顺便贴点代码,方便大家参考。

首先,ADC12DJ3200这个芯片的配置还是挺关键的,毕竟它直接决定了数据的采集质量。我们用的是单通道模式,204B接口设置为8lane,采样率6G。这个配置下,数据吞吐量还是挺大的,所以时钟和AD的配置必须得精准。

先来看看时钟芯片的配置。时钟芯片用的是LMK04828,这个芯片的配置相对复杂,但好在TI提供了配置工具,可以直接生成寄存器配置代码。下面是一段时钟芯片的配置代码:

// LMK04828配置代码

void configure_LMK04828() {

// 设置PLL1和PLL2

write_register(0x100, 0x01); // PLL1 enable

write_register(0x101, 0x02); // PLL2 enable

// 设置时钟输出

write_register(0x200, 0x03); // CLKout0 enable

write_register(0x201, 0x04); // CLKout1 enable

// 设置分频器

write_register(0x300, 0x05); // CLKout0 divider

write_register(0x301, 0x06); // CLKout1 divider

}这段代码主要是启用了PLL1和PLL2,并且配置了时钟输出和分频器。具体的寄存器地址和值需要根据实际需求来调整。

接下来是ADC12DJ3200的配置。ADC的配置主要是通过SPI接口进行的,下面是一段ADC的配置代码:

// ADC12DJ3200配置代码

void configure_ADC12DJ3200() {

// 设置采样率

write_register(0x10, 0x07); // 6G采样率

// 设置JESD204B接口

write_register(0x20, 0x08); // 8lane配置

// 设置单通道模式

write_register(0x30, 0x01); // 单通道模式

}这段代码设置了ADC的采样率、JESD204B接口的lane数以及单通道模式。同样,具体的寄存器地址和值需要根据实际需求来调整。

最后是Vivado工程的配置。Vivado 2017.4的工程配置相对简单,主要是设置时钟、IP核和约束文件。下面是一个简单的Vivado工程配置步骤:

- 创建一个新的Vivado工程,选择KU115作为目标器件。

- 添加时钟IP核,设置时钟频率为6G。

- 添加JESD204B IP核,配置为8lane,单通道模式。

- 添加约束文件,设置引脚分配和时序约束。

整个工程配置完成后,编译生成bitstream,下载到KU115上就可以开始采集数据了。

整个过程虽然有点复杂,但一步步来还是可以搞定的。希望这段代码和配置步骤能对大家有所帮助。如果有问题,欢迎留言讨论。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献7条内容

已为社区贡献7条内容

所有评论(0)