【chatgpt】几种3D堆叠结构

架构类型关键特性成本性能灵活性SoC单大芯片✅低⚠️受限❌差2.5D多Chiplet并排⚖️中✅中高✅中L3D垂直堆叠⚠️较高✅高⚠️中S3D多个小3D堆叠❌最高✅最高✅最优这张图强调的是——如何在性能、成本和封装复杂度之间做平衡选择,是现代Chiplet系统设计中的关键课题。

·

来自:Cost-Performance Co-Optimization for the Chiplet Era https://nanocad.ee.ucla.edu/wp-content/papercite-data/pdf/c131.pdf

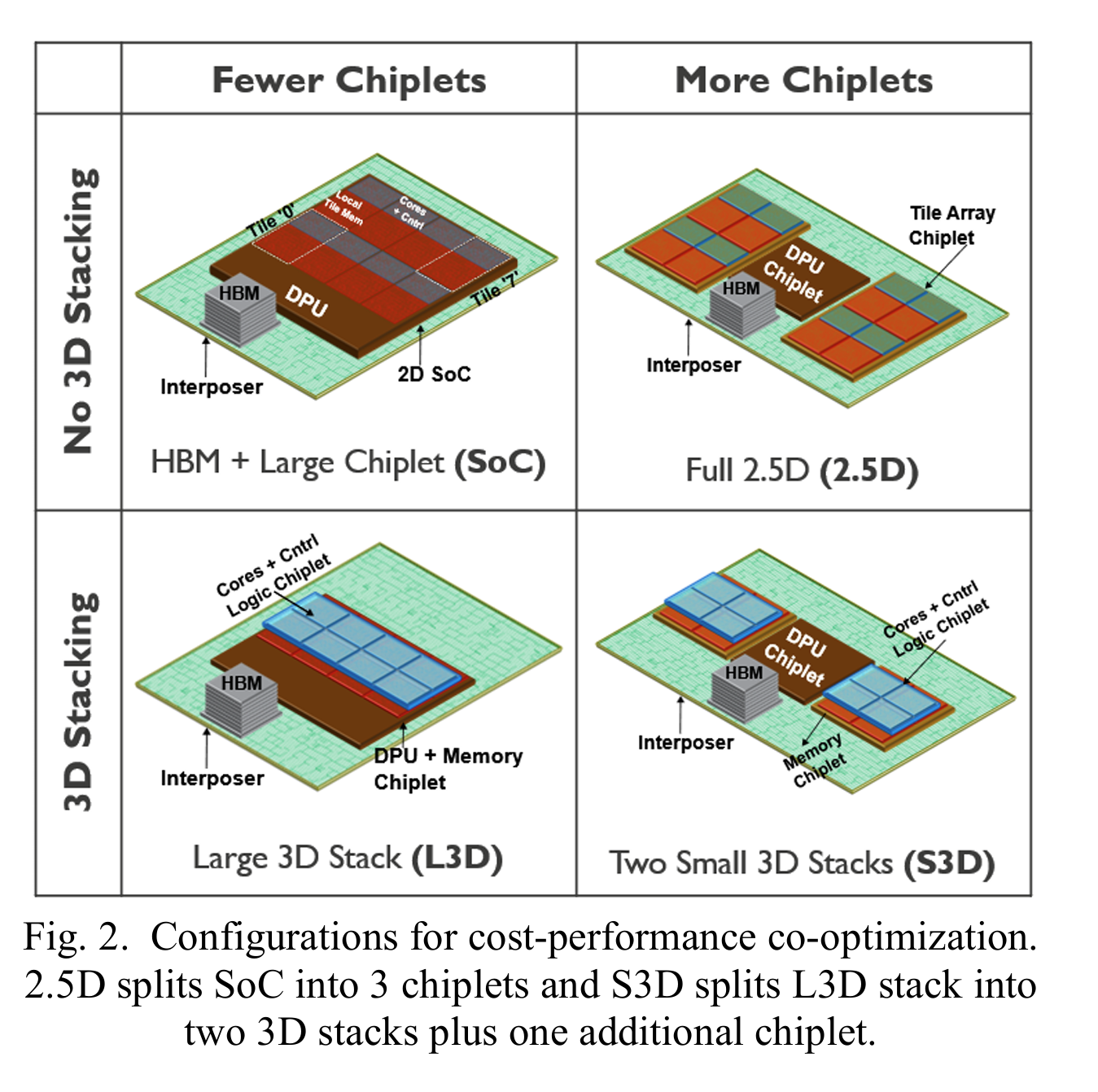

这张图展示了不同 Chiplet架构在成本与性能之间的权衡配置,通过是否使用3D堆叠技术、以及chiplet数量的变化,提出了四种典型集成方式。下面是详细解析:

🧠 图示结构总览

图中分为两大维度:

-

纵向:是否采用3D堆叠技术

- No 3D Stacking(无3D堆叠)

- 3D Stacking(有3D堆叠)

-

横向:Chiplet数量

- Fewer Chiplets(较少chiplet)

- More Chiplets(较多chiplet)

这就形成了 四种组合方式:

🟩 1. HBM + Large Chiplet (SoC) — 无3D堆叠 + 少量Chiplet

- 架构类型:传统2D SoC(系统级芯片),只有一个较大的chiplet,旁边连接HBM(高带宽存储)。

- 优势:集成度高、简单;适用于较低复杂度或成本敏感型产品。

- 缺点:可扩展性差,面积大,热管理受限。

🟧 2. Full 2.5D (2.5D) — 无3D堆叠 + 多个Chiplet

- 架构类型:多个chiplet放置在同一个interposer上(中介层),包括DPU chiplet、Tile Array chiplet等。

- 优势:灵活组合功能模块、改善良率、可实现高性能。

- 缺点:仍是单层结构,连线密度和互连带宽有限。

🟦 3. Large 3D Stack (L3D) — 有3D堆叠 + 少量Chiplet

- 架构类型:采用3D堆叠将DPU和Memory chiplet堆叠在一起,额外在上方堆叠Cores和控制逻辑。

- 优势:节省面积、提升带宽、降低功耗路径。

- 适合:需要高密度集成但chiplet数量不多的场景。

🟪 4. Two Small 3D Stacks (S3D) — 有3D堆叠 + 多个Chiplet

- 架构类型:将L3D进一步拆分为两个小堆叠单元(如DPU+Memory、Cores+Control),再加一个独立Memory chiplet。

- 优势:灵活性更高,热管理更易、可按模块分批生产。

- 代表更高级的系统封装方式,如复杂AI处理器、异构计算平台。

🔧 图注说明

“2.5D splits SoC into 3 chiplets and S3D splits L3D stack into two 3D stacks plus one additional chiplet.”

- 2.5D架构:将原本的单芯片SoC拆分为3个chiplet(DPU、Tile、HBM等)。

- S3D架构:在L3D的基础上,进一步拆解为两个较小的3D堆叠模块,再加一个独立chiplet,实现更细颗粒度的模块化。

✅ 总结

| 架构类型 | 关键特性 | 成本 | 性能 | 灵活性 |

|---|---|---|---|---|

| SoC | 单大芯片 | ✅低 | ⚠️受限 | ❌差 |

| 2.5D | 多Chiplet并排 | ⚖️中 | ✅中高 | ✅中 |

| L3D | 垂直堆叠 | ⚠️较高 | ✅高 | ⚠️中 |

| S3D | 多个小3D堆叠 | ❌最高 | ✅最高 | ✅最优 |

这张图强调的是——如何在性能、成本和封装复杂度之间做平衡选择,是现代Chiplet系统设计中的关键课题。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献31条内容

已为社区贡献31条内容

所有评论(0)