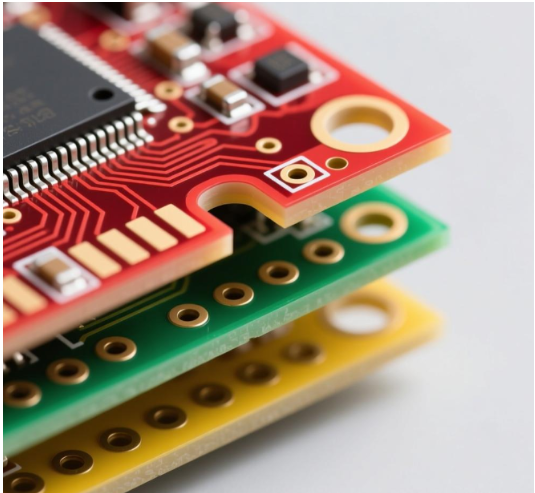

PCB叠加核心:层间结构布局与层压协同设计

信号层与接地层间距≤0.3mm(微带线)或 0.2mm(带状线),确保信号回流路径最短(减少辐射损耗),间距超 0.5mm 时,1GHz 信号损耗增加 50%。结构:Top(数字信号层)→ GND1(数字地)→ 模拟信号层 → 电源层(分割为模拟 / 数字电源)→ GND2(模拟地)→ Bottom(高频信号层)解决方案:① 采用对称结构(铜厚、层数对称);结构:Top(信号层,数字 / 低频)→

PCB叠加设计的核心是 “层间结构规划”—— 信号层、电源层、接地层的位置关系、层压顺序直接影响 PCB 的稳定性(防翘曲)、信号完整性(阻抗匹配)、生产可行性(层压良率)。若结构布局不当,会导致层压后翘曲度超 1%(无法安装)、电源阻抗超标(≥20mΩ)、信号串扰加剧(-25dB)。今天,我们解析层间结构的核心设计原则、经典布局方案、层压顺序要求与常见问题解决方案,帮你实现层间协同优化。

一、层间结构设计三大核心原则

功能分区原则:同类层相邻,减少干扰耦合 —— 电源层与接地层必须相邻(形成 “电源 - 地” 耦合对,降低阻抗),模拟信号层与数字信号层之间隔接地层(避免数字噪声耦合至模拟信号);

对称结构原则:层压结构需上下对称,防止翘曲 —— 如 6 层板对称结构 “Top - 信号 - GND - 电源 - GND - 信号 - Bottom”,上下层材质、铜厚一致(1oz 铜),层压后翘曲度≤0.6%,非对称结构翘曲度可达 1.2%;

信号层贴近地原则:信号层与接地层间距≤0.3mm(微带线)或 0.2mm(带状线),确保信号回流路径最短(减少辐射损耗),间距超 0.5mm 时,1GHz 信号损耗增加 50%。

二、经典层间布局方案(按层数分类)

1. 4 层板(最通用)

-

结构:Top(信号层,数字 / 低频)→ GND(完整接地层)→ 电源层(单一 / 分割电源)→ Bottom(信号层,模拟 / 高频)

-

核心优势:电源与地相邻(间距 0.2mm),电源阻抗≤15mΩ;信号层上下均有参考地,串扰 - 33dB;

-

设计要点:① 电源层面积≥PCB 面积的 30%,确保供电均匀;② 模拟信号优先走 Bottom 层(远离数字信号);③ 层压顺序:Top - 介质 - GND - 介质 - 电源 - 介质 - Bottom(对称层压)。

2. 6 层板(抗干扰优先)

-

结构:Top(数字信号层)→ GND1(数字地)→ 模拟信号层 → 电源层(分割为模拟 / 数字电源)→ GND2(模拟地)→ Bottom(高频信号层)

-

核心优势:数字与模拟信号层隔接地层,串扰≤-38dB;双接地层增强屏蔽,EMC 性能提升;

-

设计要点:① GND1 与 GND2 通过多个过孔(间距≤5mm)连接,形成完整接地网络;② 电源层分割间距≥2mm,避免不同电压串扰;③ 层压顺序对称(Top 与 Bottom 材质 / 铜厚一致),防翘曲。

3. 8 层板(高密高频场景)

-

结构:Top(高频信号层,如 PCIe)→ GND1 → 数字信号层 → 电源层(主电源)→ GND2 → 模拟信号层 → GND3 → Bottom(高频信号层)

-

核心优势:高频信号层上下为接地层(带状线结构),辐射损耗≤0.5dB/m;模拟与数字完全隔离,串扰 - 40dB;

-

设计要点:① 三个接地层通过过孔阵列(间距≤3mm)连通,接地阻抗≤5mΩ;② 高频信号层介质选用低损耗基材(如罗杰斯 4350B),减少介质损耗。

三、层压顺序与介质层选择

层压顺序要求:① 对称层压:上下层的铜厚、介质厚度必须一致(如 Top 铜厚 1oz,Bottom 也为 1oz),避免层压时应力不均;② 核心层优先:电源层、接地层作为核心层,夹在中间,信号层作为外层,便于焊接;③ 介质层均匀:各介质层厚度偏差≤±10%(如设计 0.2mm,实际 0.18-0.22mm),避免阻抗波动。

介质层选择:① 普通场景(≤5GHz):FR-4 基材(εr=4.4,tanδ=0.02),介质厚度 0.1-0.3mm;② 高频场景(>5GHz):罗杰斯 4350B(εr=3.48,tanδ=0.0037),介质厚度 0.127-0.254mm;③ 电源层与地间距:优先选 0.1-0.2mm(降低阻抗),若需控制阻抗(如 50Ω),可按公式调整(介质厚度 h=Z0×√εr/60,Z0 为目标阻抗)。

四、常见结构问题与解决方案

-

问题 1:层压后翘曲(超 0.75%)

原因:结构不对称(如 Top 铜厚 1oz,Bottom 0.5oz)、层压温度梯度大;

解决方案:① 采用对称结构(铜厚、层数对称);② 层压时缓慢升温(1℃/min),保温 90 分钟;③ 增加接地层厚度(2oz 铜),增强刚性。

-

问题 2:电源阻抗超标(≥20mΩ)

原因:电源层与地间距过大(>0.3mm)、电源层面积过小(<20% PCB 面积);

解决方案:① 缩小电源与地间距至 0.15mm;② 电源层面积扩展至 PCB 面积的 40%;③ 在电源层添加去耦电容过孔(间距≤10mm),降低局部阻抗。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)