每日一篇读懂vivado时序报告2——General Information解析

本文介绍了FPGA时序报告的基本分析流程。首先需要准备FPGA工程并打开Vivado工具的时序报告功能。重点解读了General Information中的三部分关键内容:1)器件参数(型号7z020、封装clg400、速度等级-2);2)Vivado软件版本信息(2022.2版);3)时序报告生成命令及其参数意义(包括路径数量限制、详细检查模式等)。这些信息共同构成了时序分析的基础框架,为后续深

目录

3.1 Part: Device=7z020 Package=clg400 Speed=-2

1.FPGA工程准备

首先,我们准备一个FPGA工程,内容参考如下博文:

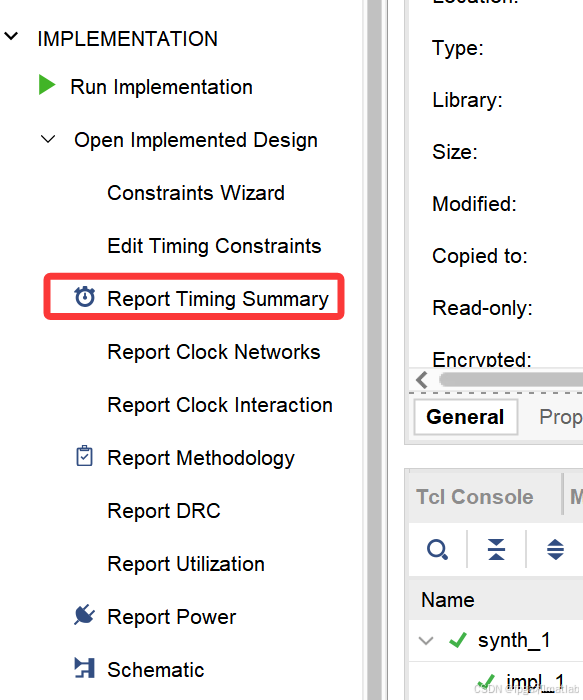

2.打开时序报告

我们点击如下的按键:

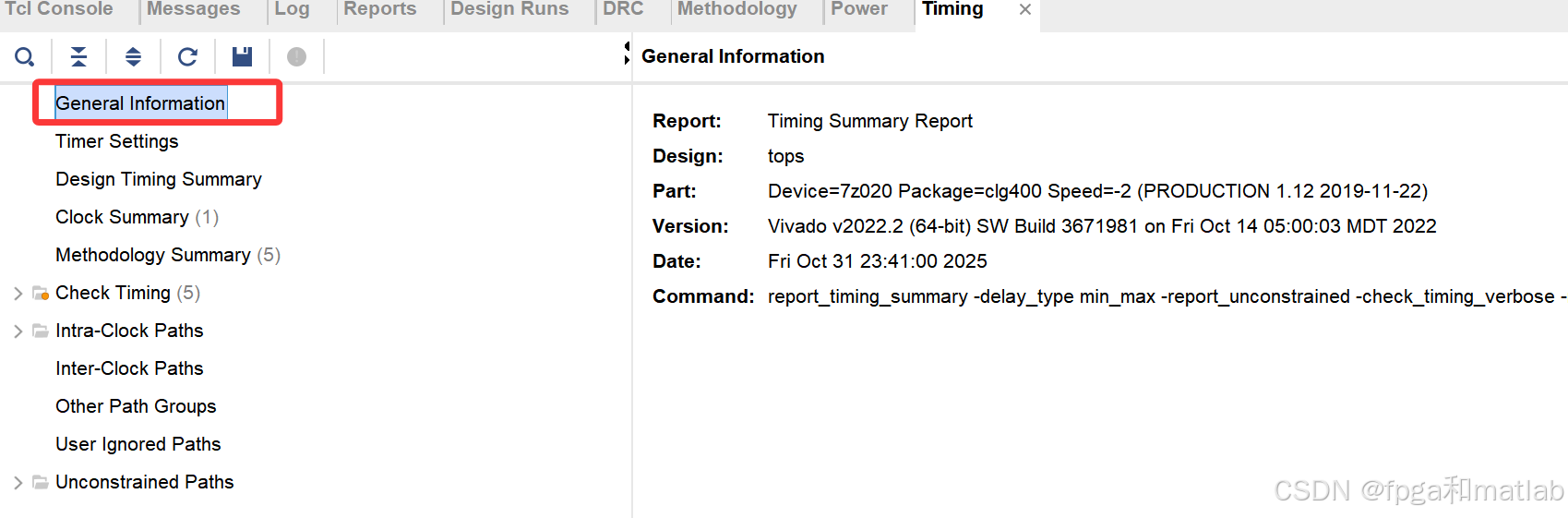

然后我们点击如下按键:

我们可以看到General Information的信息。

3.General Information信息解读

根据上述的截图内容,我们逐个进行介绍:

3.1 Part: Device=7z020 Package=clg400 Speed=-2

Part: Device=7z020 Package=clg400 Speed=-2 (PRODUCTION 1.12 2019-11-22)

这部分是器件与封装的关键信息,每一项都对时序性能有直接影响:

Device=7z020:指所使用的FPGA器件型号为“Xilinx Zynq-7000系列的xc7z020”。Zynq-7000是 Xilinx的异构SoC(片上系统),集成了ARM Cortex-A9处理器和FPGA逻辑资源,“020”代表其逻辑资源规模(约20K逻辑单元),资源规模决定了设计的复杂度上限,也间接影响时序收敛难度(资源越密集,布线延迟可能越大)。

Package=clg400:表示器件的封装类型为“clg400”,即400引脚的陶瓷栅格阵列封装。封装类型决定了引脚的数量、布局和电气特性,进而影响信号的扇出、布线长度和时序延迟(如引脚到内部逻辑的走线长度差异会导致延迟波动)。

Speed=-2:是器件的速度等级,“-2”代表该器件的时序性能等级(数值越小,速度越快)。速度等级本质是器件生产工艺的 “筛选等级”—— 同一型号器件会因工艺偏差分为不同速度等级,-2等级的器件内部逻辑单元、布线资源的延迟更小,能支持更高的工作频率。

(PRODUCTION 1.12 2019-11-22):是器件的生产版本信息,“PRODUCTION”表示量产版本,“1.12”是版本号,“2019-11-22”是生产批次日期。版本信息反映了器件的工艺成熟度,后续若出现时序问题,可结合版本追溯是否为工艺迭代导致的差异。

3.2 Version: Vivado v2022.2

Version: Vivado v2022.2 (64-bit) SW Build 3671981 on Fri Oct 14 05:00:03 MDT 2022

这部分是设计工具的版本信息:

Vivado v2022.2 (64-bit):说明使用的是Xilinx Vivado Design Suite 2022.2版本的64位软件。Vivado是Xilinx FPGA/SoC的主流设计工具,集成了设计输入、综合、实现、时序分析、比特流生成等全流程功能。版本号“2022.2”代表其发布时间和功能迭代节点,不同版本在时序分析算法、约束支持、器件适配等方面存在差异。

SW Build 3671981 on Fri Oct 14 05:00:03 MDT 2022:是软件的编译构建信息,“Build 3671981” 是构建编号,“Fri Oct 14 05:00:03 MDT 2022”是构建时间。这些信息主要用于技术支持——若设计中出现工具相关的异常(如时序报告bug、功能适配问题),可通过构建编号和时间向Xilinx官方追溯问题根源。

3.3 Command

Command: report_timing_summary -delay_type min_max -report_unconstrained -check_timing_verbose -max_paths 10 -input_pins -routable_nets -name timing_1

这是生成时序报告的具体命令及参数,每个参数都定义了报告的分析范围和呈现方式:

report_timing_summary:是Vivado中用于生成“时序摘要报告”的核心命令,它会遍历设计中的时序路径,汇总关键时序指标。

-delay_type min_max:指定时序分析的延迟类型为“min_max”,即同时分析“最小延迟”和“最大延迟”。

-report_unconstrained:表示报告中会包含“无约束的时序路径”。在时序分析中,“约束”是设计者对关键路径的频率、延迟等要求(如create_clock、set_input_delay等命令);无约束的路径若未被显式约束,工具会默认其不需要满足特定时序要求,但仍会分析其固有延迟,这一参数可帮助设计者识别 “遗漏约束的关键路径”,避免因约束不全导致时序隐患。

-check_timing_verbose:启用详细的时序检查模式,会输出更多时序分析的中间信息(如路径的逻辑层级、布线延迟、单元延迟等细分项),便于设计者深入 debug 时序问题。

-max_paths 10:指定报告中最多呈现10条关键时序路径。“关键路径” 是指时序裕量最小(最紧张)的路径,分析这些路径可快速定位设计中时序最薄弱的环节。

-input_pins:表示报告中会包含 “输入引脚” 相关的时序路径。输入引脚是设计与外部系统的接口,其输入延迟(input_delay)会直接影响内部时序路径的建立 / 保持时间,分析这些路径可确保外部输入信号与内部时钟的时序兼容性。

-routable_nets:表示报告中会包含“可布线的网络”相关时序信息。“可布线网络”是指设计中实际完成物理布线的信号网络,其布线延迟是时序延迟的重要组成部分(尤其在FPGA中,布线资源的延迟占比可达50%以上),分析这些网络可反映物理实现后的真实时序性能。

-name timing_1:为该时序报告指定名称为“timing_1”,便于在Vivado界面中区分多个时序报告。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献41条内容

已为社区贡献41条内容

所有评论(0)