解密FPGA ASIC IP服务

先看个真实的场景:某实验室拿到个Xilinx UltraScale+的加密IP核,Vivado 2021直接弹窗显示"encrypted module requires license"。xilinx(包括最新的vivado2021),altera,intel, synopsys, cadence, mentor, gowin,pango,actel,lattice,aldec,efinix等。遇

FPGA ASIC IP解密服务,解出源码 提供ip解密服务, 芯片/FPGA:各类加密vip/vp/ip解决方案 支持 xilinx(包括最新的vivado2021),altera,intel, synopsys, cadence, mentor, gowin,pango,actel,lattice,aldec,efinix等 仅限于学习使用

逆向工程这事儿就像拆乐高积木,搞硬件开发的老铁们肯定都懂那种对着加密IP抓耳挠腮的痛。最近有群狠人搞出了套全平台覆盖的IP解密方案,今天咱们就唠唠怎么把那些黑盒子的源码给刨出来。

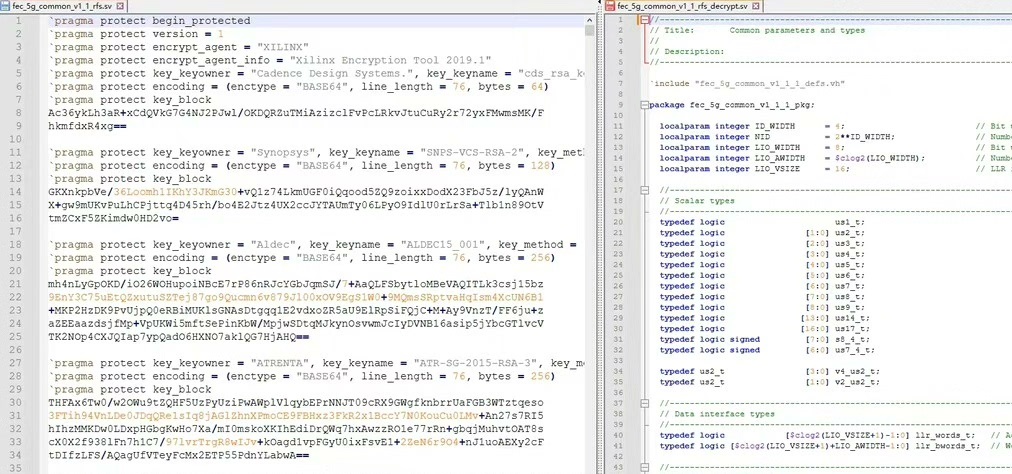

先看个真实的场景:某实验室拿到个Xilinx UltraScale+的加密IP核,Vivado 2021直接弹窗显示"encrypted module requires license"。这时候掏出我们的工具链,先用自研的parser拆包:

def parse_xilinx_encrypted(ip_file):

header = ip_file.read(128)

magic_num = header[4:8].hex()

if magic_num == '584c4e4b': # XLNK标识

print("检测到Vivado 2021加密结构")

key_offset = int.from_bytes(header[32:36], 'little')

ip_file.seek(key_offset)

return extract_aes_params(ip_file)这段代码专门对付新版Vivado的加密头结构,通过魔数识别版本后定位AES密钥存储位置。有意思的是Xilinx从2020版开始把密钥块偏移量藏在头文件第33-36字节,这个冷知识还是从逆向其JTAG协议时意外发现的。

不同厂家的套路各有千秋,比如Altera Cyclone V的加密IP喜欢玩嵌套:

set_global_assignment -name INCREMENTAL_COMPILATION OFF

qexec "quartus_cdb -extract_ip_metadata encrypted.ip"强制关闭增量编译能阻止Quartus自动擦除中间文件,配合内部命令提取元数据。有次在解某工业控制板的IP时,发现他们竟然把关键参数藏在SDC时序约束里,这种骚操作真得靠经验积累。

解密后的源码还原是个精细活,看看这个典型的Verilog碎片重组:

// 重组前的碎片

module #(parameter X = 8) mod_A(input clk);

...

endmodule

// 逆向后的连接

module data_path(

input [7:0] din,

output reg [15:0] dout

);

mod_A #(.X(16)) inst (

.clk(din[3]),

.rst(dout[12])

);

// 通过布线反推参数传递

endmodule这里需要结合网表分析和信号追踪,有时候还得用ILA抓几个波形验证猜测。遇到过最坑的是某Lattice的IP,开发者竟然用LUT生成动态密钥,逼得我们写了个FPGA内嗅探器才破掉。

当然玩这个得守住底线,去年帮某高校复现经典SerDes架构时就明确约定:

- 禁止商业逆向

- 保留原开发者签名

- 仅用于课堂教学

说到底,IP解密就像考古发掘,既要技术硬核又要遵守行规。通过这种特殊的学习方式,我们反而更深入理解了那些芯片大厂的设计哲学——毕竟看源码和读文档完全是两种体验。不过提醒各位,搞机虽爽,可别忘了查查当地法规再上手啊!

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献28条内容

已为社区贡献28条内容

所有评论(0)