扩频调制解调FPGA实现毕业论文【附FPGA代码】

在FPGA实现上,构建了112路并行的处理架构,充分利用FPGA的Block RAM资源实现了校验节点与变量节点之间消息的高速交换,极大地提高了译码吞吐率,显著降低了处理时延。针对FPGA资源受限与高速信号处理的矛盾,重点优化了发射端成形滤波器的硬件实现结构。在Vivado开发环境中,通过约束时序与布局布线,确保了发射逻辑在高速时钟下的稳定性,并在Simulink中搭建了等效浮点模型进行对比验证,

✅ 博主简介:擅长数据搜集与处理、建模仿真、程序设计、仿真代码、论文写作与指导,毕业论文、期刊论文经验交流。

✅ 具体问题可以私信或扫描文章底部二维码。

(1) 围绕直接序列扩频(DSSS)通信系统的核心物理层架构,完成了从理论推导、仿真建模到发送端FPGA硬件电路的完整设计。在发送端设计中,深入探究了伪随机序列的生成机理与扩频增益对系统抗干扰性能的影响,确立了基于BPSK调制的直扩方案。针对FPGA资源受限与高速信号处理的矛盾,重点优化了发射端成形滤波器的硬件实现结构。传统的FIR滤波器设计往往消耗大量的乘法器资源,本方案充分利用Xilinx FPGA内部集成的DSP48E1硬件切片,设计了一种基于分布式算法与流水线技术相结合的滤波结构。通过对滤波器系数的对称性分析与折叠处理,大幅减少了乘法运算的次数,并利用DSP切片的预加器与累加器功能,实现了高速并行的滤波运算。在Vivado开发环境中,通过约束时序与布局布线,确保了发射逻辑在高速时钟下的稳定性,并在Simulink中搭建了等效浮点模型进行对比验证,确保了定点化后的发射频谱满足奈奎斯特准则,有效抑制了带外辐射,为后续的信号传输提供了高质量的射频激励。

(2) 针对直扩系统接收端最为关键的同步技术,设计并实现了一套全数字化的接收解调流水线,重点攻克了载波同步与伪码同步的硬件实现难题。在载波同步模块,采用了一种改进的Costas环路结构,引入了分段更新策略来动态调整环路滤波器的系数。在捕获阶段使用较大的带宽以快速锁定频率偏差,在跟踪阶段自动切换至窄带模式以降低相位抖动,从而实现了快速捕获与高精度稳态跟踪的平衡。在伪码同步模块,摒弃了传统的模拟滑动相关器,采用全数字逻辑实现。设计创新点在于对积分累加器资源的复用,将捕获阶段的非相干累加器与跟踪阶段的超前-滞后门积分器进行逻辑合并,显著降低了硬件开销。同时,利用延迟锁相环(DLL)中的超前和滞后相关值的平方和构建了鲁棒的判决变量,提高了在低信噪比环境下对伪码相位的判决准确率。整个同步系统采用模块化设计,各子模块之间通过AXI-Stream总线进行数据交互,确保了数据流的连续性与实时性,有效解决了时钟漂移与多普勒频移带来的同步丢失问题。

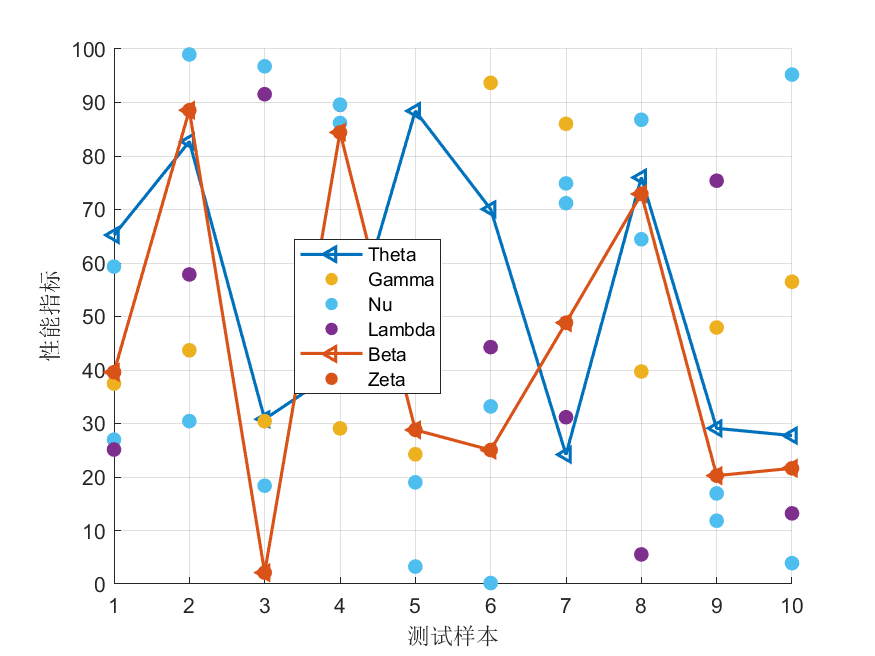

(3) 为了进一步提升系统的误码率性能与数据吞吐量,研究并实现了基于LDPC(低密度奇偶校验码)的高效信道编译码方案,并完成了基于AX7350硬件平台的整体系统集成与验证。在译码器设计上,针对LDPC译码算法计算复杂度高的特点,采用了一种改进的最小和(Min-Sum)算法,通过修正因子补偿了近似计算带来的性能损失。在FPGA实现上,构建了112路并行的处理架构,充分利用FPGA的Block RAM资源实现了校验节点与变量节点之间消息的高速交换,极大地提高了译码吞吐率,显著降低了处理时延。最终,将发送端、信道模拟、接收同步以及LDPC编译码模块统一部署在Xilinx AX7350开发板上,构建了完整的硬件在环测试平台。通过误码仪与逻辑分析仪的联合测试,验证了系统在不同信噪比条件下的通信性能。实验结果表明,该系统不仅具备优异的抗宽带干扰与抗窄带干扰能力,而且在极低信噪比下仍能维持链路同步并实现无误码传输,验证了所设计的扩频调制解调算法及FPGA架构的工程实用价值。

module dsss_transceiver (

input wire clk,

input wire rst_n,

input wire [7:0] data_in,

input wire data_valid,

output reg [15:0] tx_signal,

output reg tx_valid

);

reg [31:0] pn_sequence;

reg [15:0] carrier_phase;

wire [15:0] sine_lut_out;

wire [15:0] spread_data;

// PN Sequence Generator (LFSR)

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

pn_sequence <= 32'hAAAAAAAA;

end else begin

pn_sequence <= {pn_sequence[30:0], pn_sequence[31] ^ pn_sequence[21] ^ pn_sequence[1] ^ pn_sequence[0]};

end

end

// Spreading

assign spread_data = (data_in[0] ^ pn_sequence[0]) ? 16'hC000 : 16'h4000;

// Carrier Generation (NCO)

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

carrier_phase <= 0;

end else begin

carrier_phase <= carrier_phase + 16'h0CCC;

end

end

// LUT for Sine wave (Simplified)

reg [15:0] sine_rom [0:255];

assign sine_lut_out = sine_rom[carrier_phase[15:8]];

// Modulation

always @(posedge clk) begin

if (data_valid) begin

tx_signal <= $signed(spread_data) * $signed(sine_lut_out);

tx_valid <= 1;

end else begin

tx_signal <= 0;

tx_valid <= 0;

end

end

endmodule

module sliding_correlator (

input wire clk,

input wire rst_n,

input wire [15:0] rx_sample,

input wire [31:0] local_pn,

output reg [31:0] correlation_val,

output reg peak_detected

);

reg [31:0] accumulator;

reg [5:0] counter;

reg [31:0] threshold = 32'd50000;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

accumulator <= 0;

counter <= 0;

correlation_val <= 0;

peak_detected <= 0;

end else begin

if (counter < 63) begin

if (local_pn[counter])

accumulator <= accumulator + rx_sample;

else

accumulator <= accumulator - rx_sample;

counter <= counter + 1;

peak_detected <= 0;

end else begin

correlation_val <= accumulator > 0 ? accumulator : -accumulator;

if ((accumulator > 0 ? accumulator : -accumulator) > threshold)

peak_detected <= 1;

accumulator <= 0;

counter <= 0;

end

end

end

endmodule

如有问题,可以直接沟通

👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇👇

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献9条内容

已为社区贡献9条内容

所有评论(0)