DDS的IP核使用

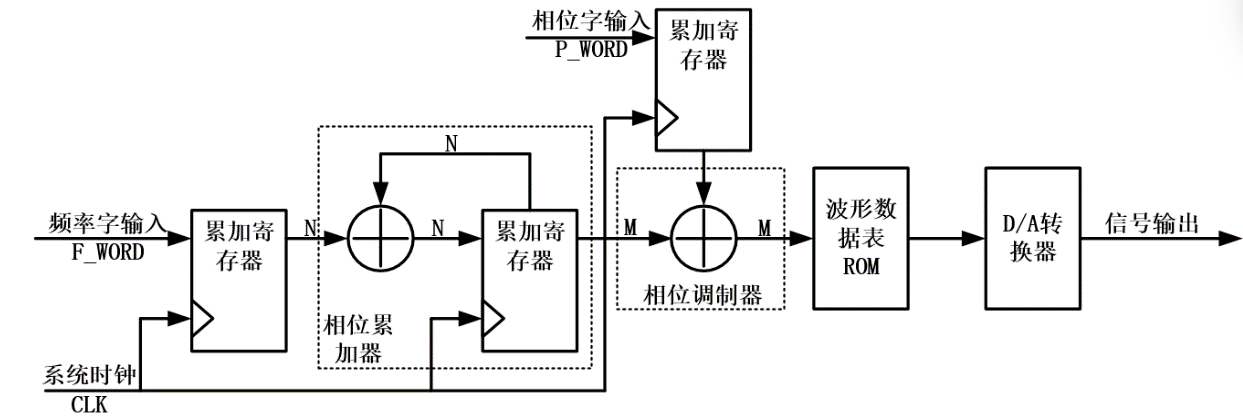

DDS(Direct Digital Synthesis,直接数字频率合成),作为信号发生器使用。使用vivado调用DDS的ip核进行仿真。设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。DDS的基本结构主要由相位累加器、相位调制器、波形数据表ROM、D/A转换器等四大结构组成,其中较多设计还会在数模转换器之后增

DDS(Direct Digital Synthesis,直接数字频率合成),作为信号发生器使用。

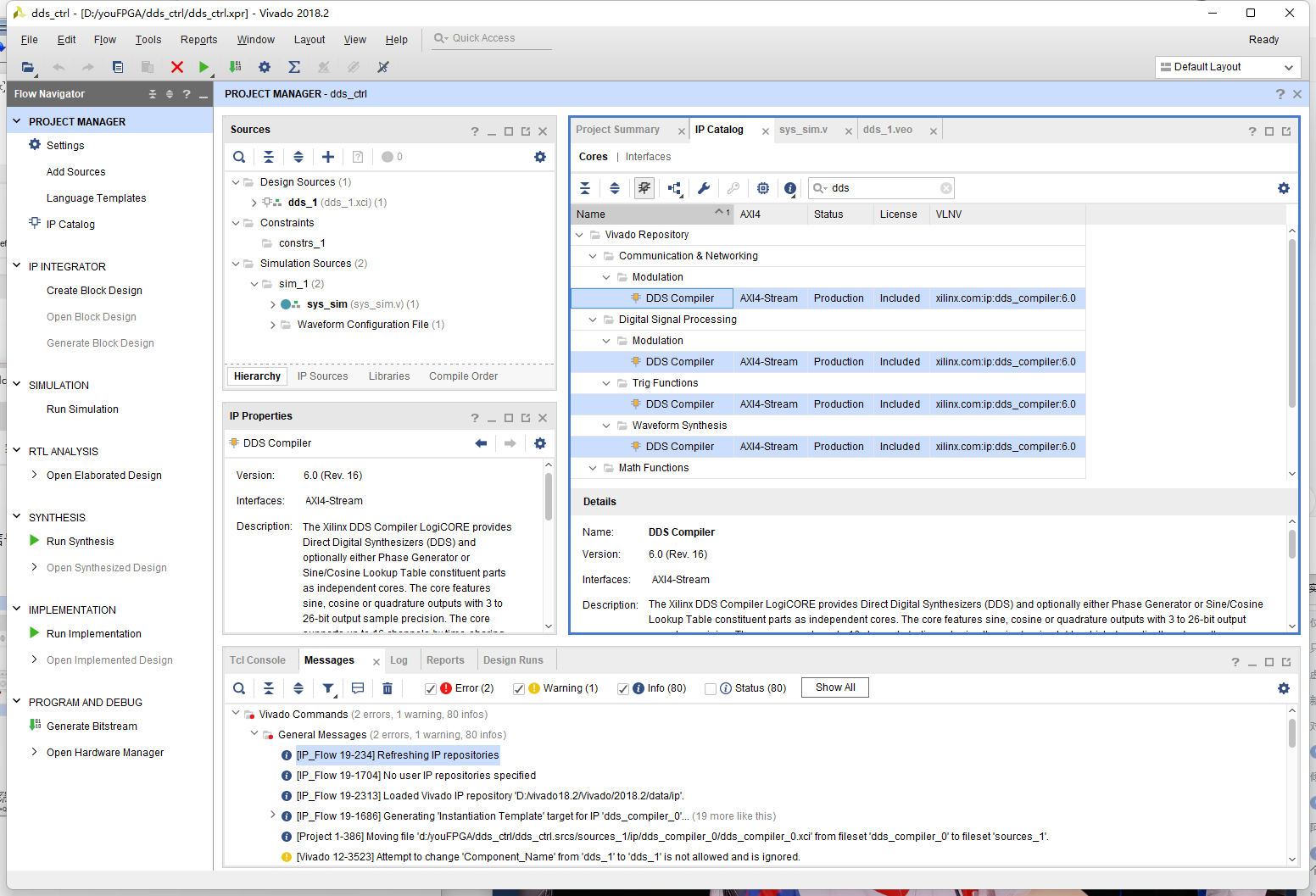

使用vivado调用DDS的ip核进行仿真。

设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

DDS的基本结构主要由相位累加器、相位调制器、波形数据表ROM、D/A转换器等四大结构组成,其中较多设计还会在数模转换器之后增加一个低通滤波器。

系统时钟CLK为整个系统的工作时钟,频率为fCLK;频率字输入F_WORD,一般为整数,数值大小控制输出信号的频率大小,数值越大输出信号频率越高,反之,输出信号频率越低,后文中用K表示;相位字输入P_WORD,为整数,数值大小控制输出信号的相位偏移,主要用于相位的信号调制,后文用P表示;设输出信号为CLK_OUT,频率为fOUT。

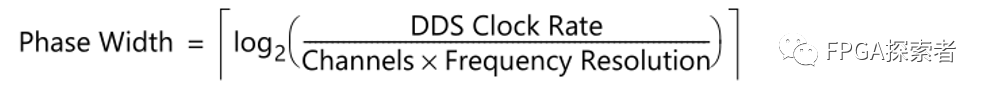

相位累加器是整个DDS的核心,在这里完成相位累加,生成相位码。相位累加器的输入为频率字输入K,表示相位增量,设其位宽为N,满足等式K = 2N * FOUT / FCLK 。其在输入相位累加器之前,在系统时钟同步下做数据寄存,数据改变时不会干扰相位累加器的正常工作。

相位调制器接收相位累加器输出的相位码, 在这里加上一个相位偏移值P,主要用于信号的相位调制,如应用于通信方面的相移键控等,不使用此部分时可以去掉,或者将其设为一个常数输入,同样相位字输入也要做寄存。

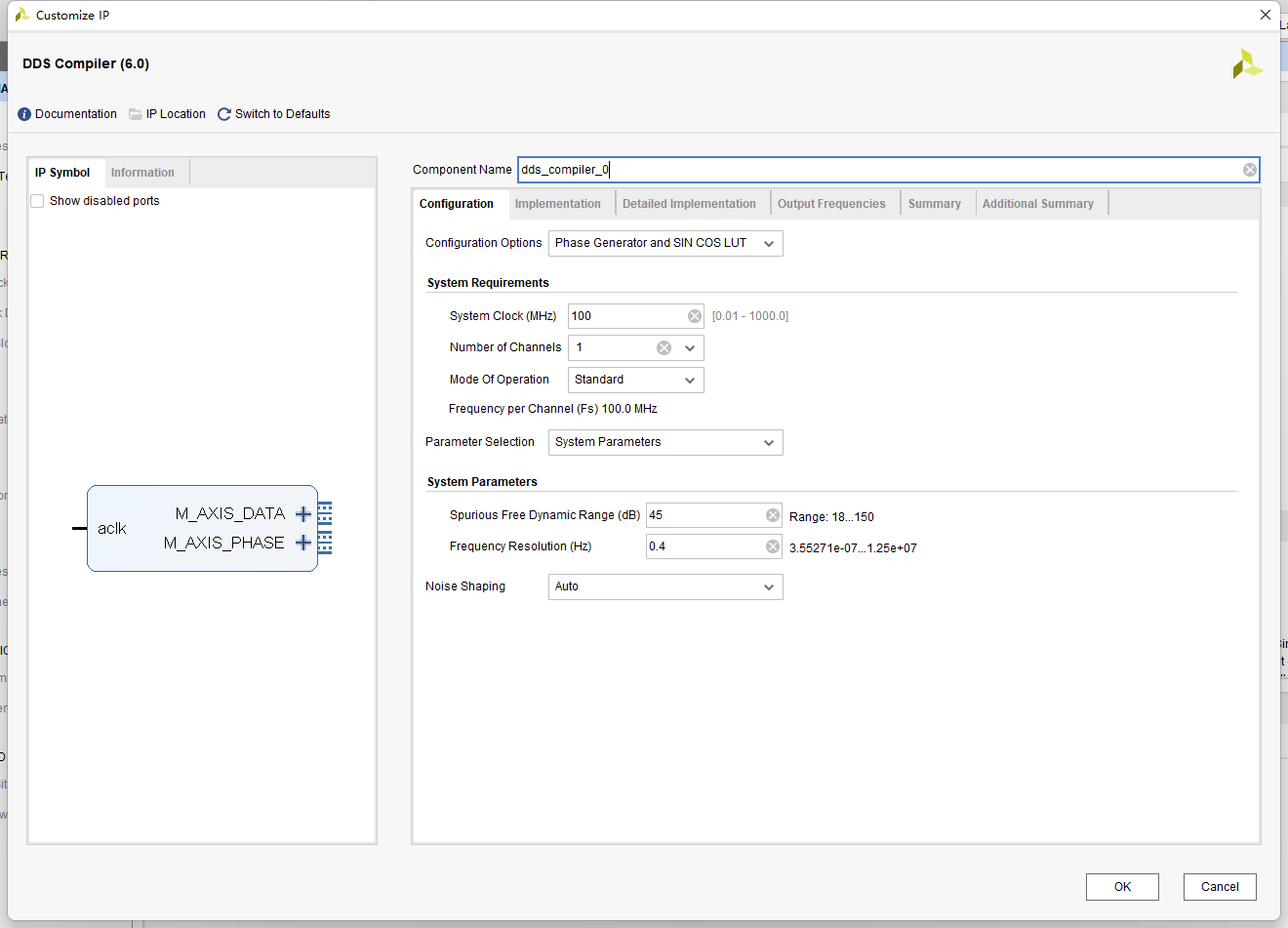

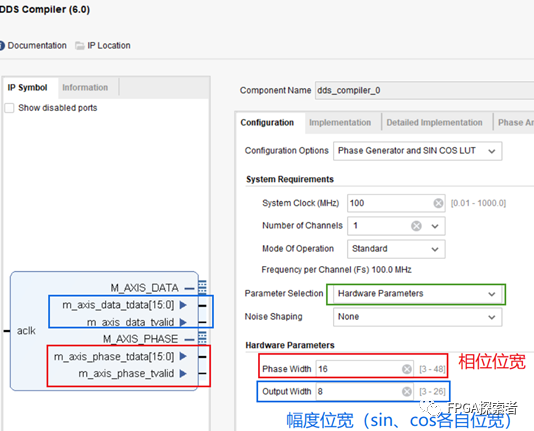

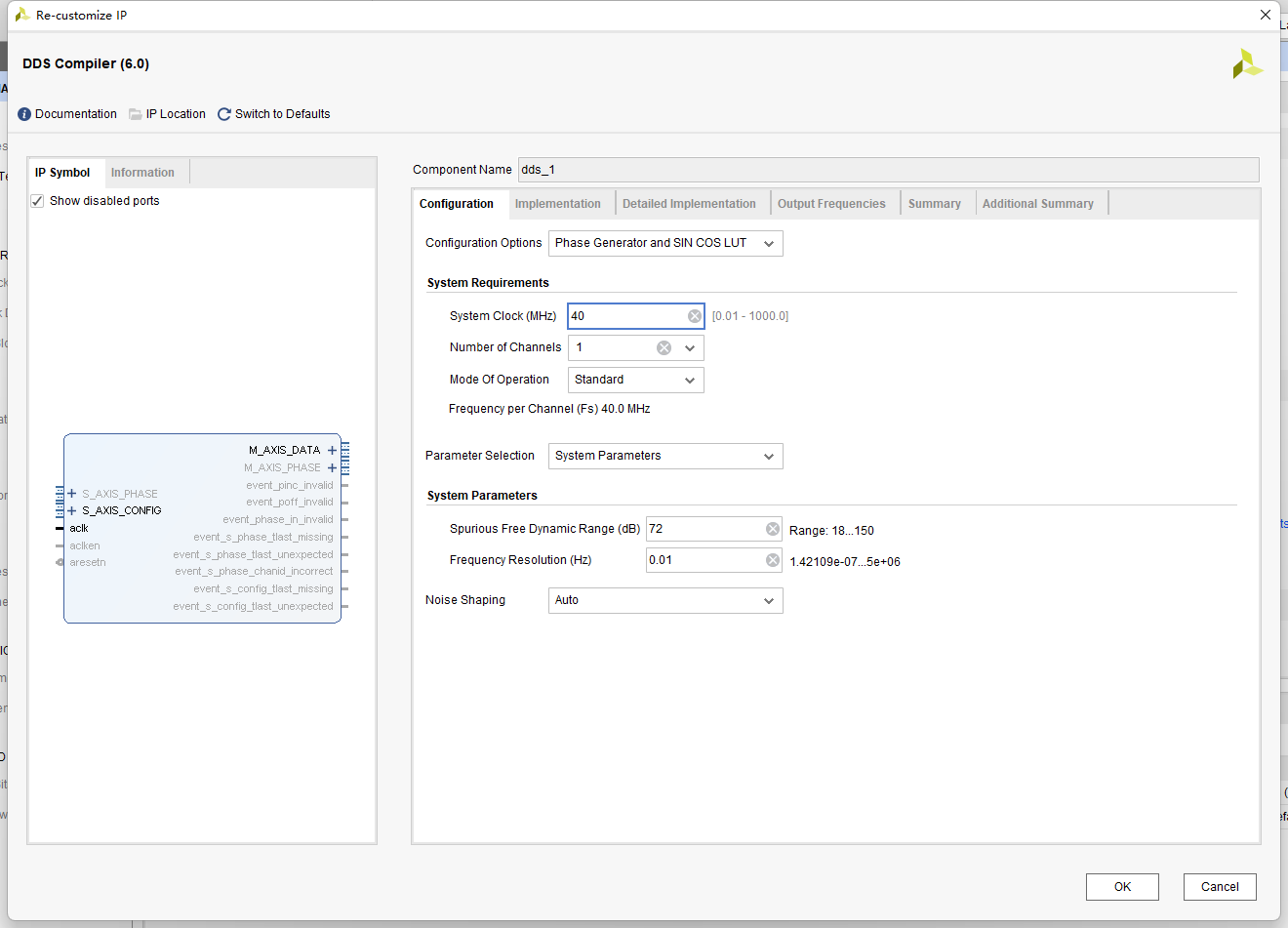

1:配置选项

三种模式可选(相位发生器+sin/cos波形发生器、仅有相位发生器、仅有sin/cos波形发生器);

2:运行时钟aclk;

100 MHz工作时钟,即100MHz采样率。

3:通道个数;

设为1,单通道模式,通道的采样频率等于采样时钟100MHz,当设为多个通道时,每个通道的采样率为工作时钟/通道数,比如4通道100MHz时钟,每个通道采样率25MHz。

4:操作模式;

Standard标准模式(常用),Rasterized栅格模式。两种情况下,输出的频率和频率分辨率、相位增量等参量的计算方式不同。

Standard Mode 和 Rasterized Mode在实现指定频率、幅度的信号时,输出没有太大的差别,两者均能满足要求,一般使用Standard配置方便。

主要的区别:

Standard模式下计算出来的相位增量可能是小数,而在FPGA中要对相位进行截断取整,存在相位误差,对噪声要求较高的场合,可以使用8处的噪声整形配置来弥补,使用相位抖动(Phase Dithering)或者泰勒级数纠正(Taylor Series Correct)来补偿相位误差;

Rasterized Mode配置下,相位增量一定是整数,不存在截断效应,没有Standard模式下的时间基抖动。

5:参数选项(System parameters、Hardware parameters)

(1) System parameters

(2) Hardware parameters

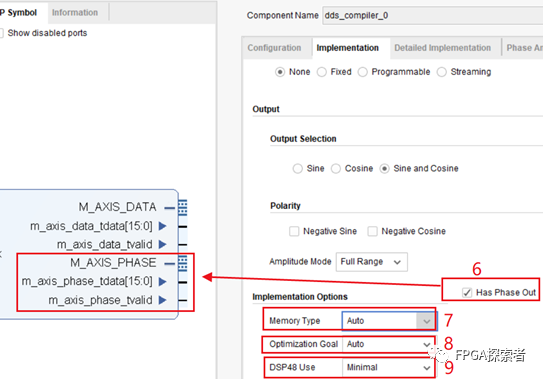

6、7、8处配置系统参数System parameters,其中:

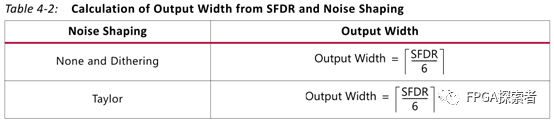

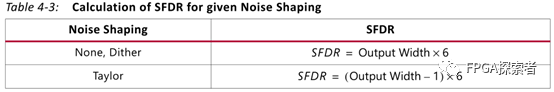

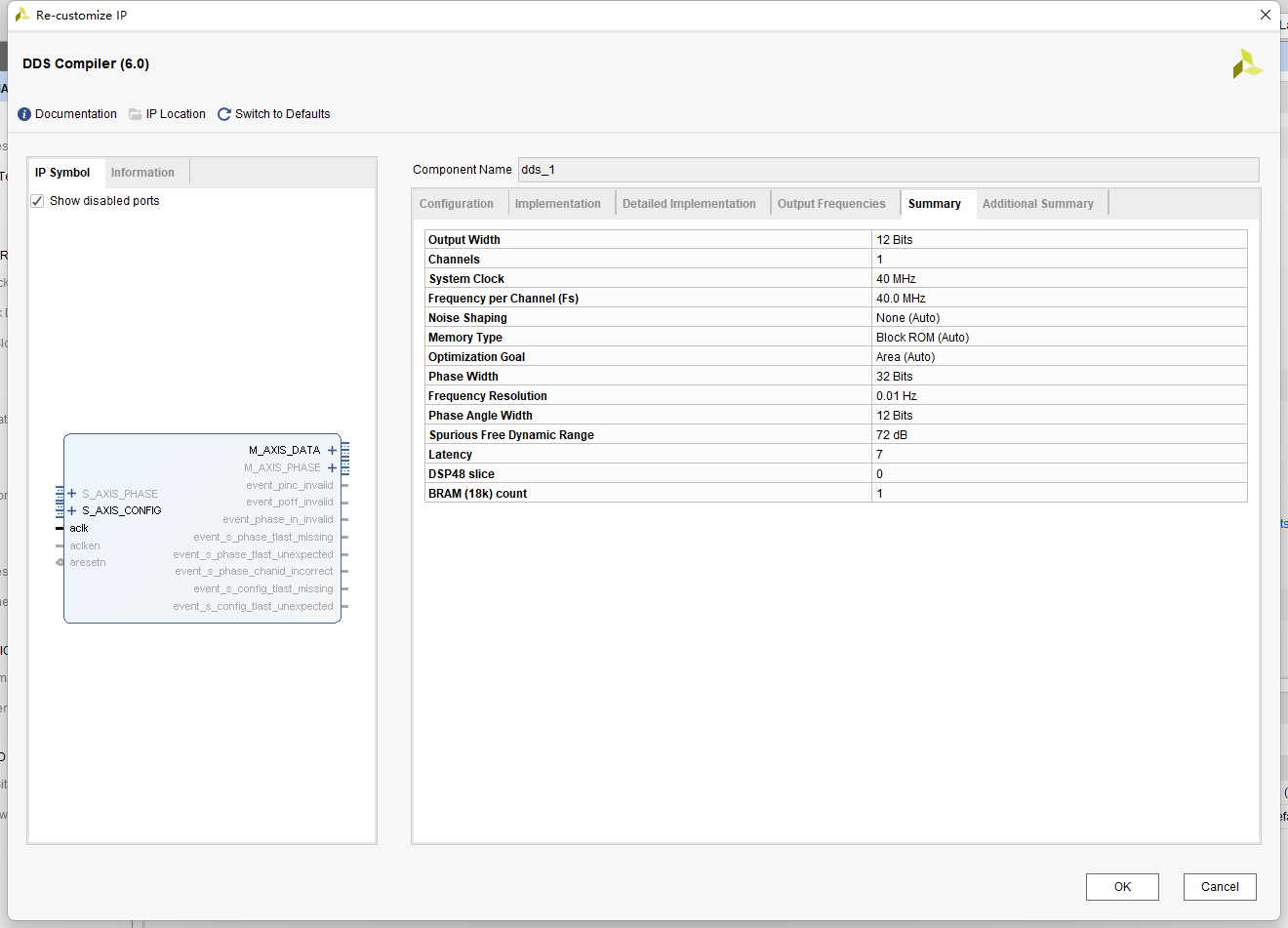

6:配置SFDR无杂散动态范围

SFDR(Spurious Free Dynamic Range,无杂散动态范围),对应幅度,对应M_AXIS_DATA通道,SFDR越大,用于表示幅度的数据的位宽越大;

如下图所示计算输出位宽,当使用SFDR = 96 dB,配置8处的噪声整形位None或者Dithering时,输出位宽位96/6=16位,向上取整后为16位;使用SFDR = 95 dB,95/6=15.83,向上取整为16位。

7:配置频率分辨率

对应相位的增量配置、位宽,对应M_AXIS_PHASE通道,频率分辨率越小,用于表示相位的数据的位宽越大;

8:配置噪声整形

4处配置成Standard标准模式时才会使用噪声整形,Auto根据设计的SFDR参数自动选择是否使用整形;None不整形;Phase Dithering相位抖动,在使用相位截断技术时,产生随机的噪声来使得量化误差随机;Taylor Series Correct 泰勒级数校正;

4处配置成Rasterized时,不存在相位误差,只能配置None。

9:Hardware parameters

这种模式下直接配置输出的位宽,但是具体输出对应的SFDR和频率分辨率会在Summary中体现,也可以自行计算。

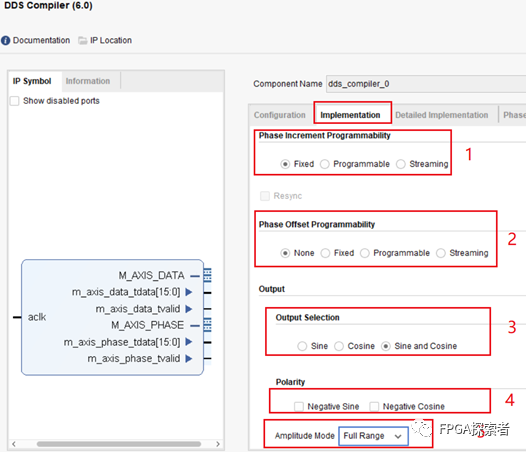

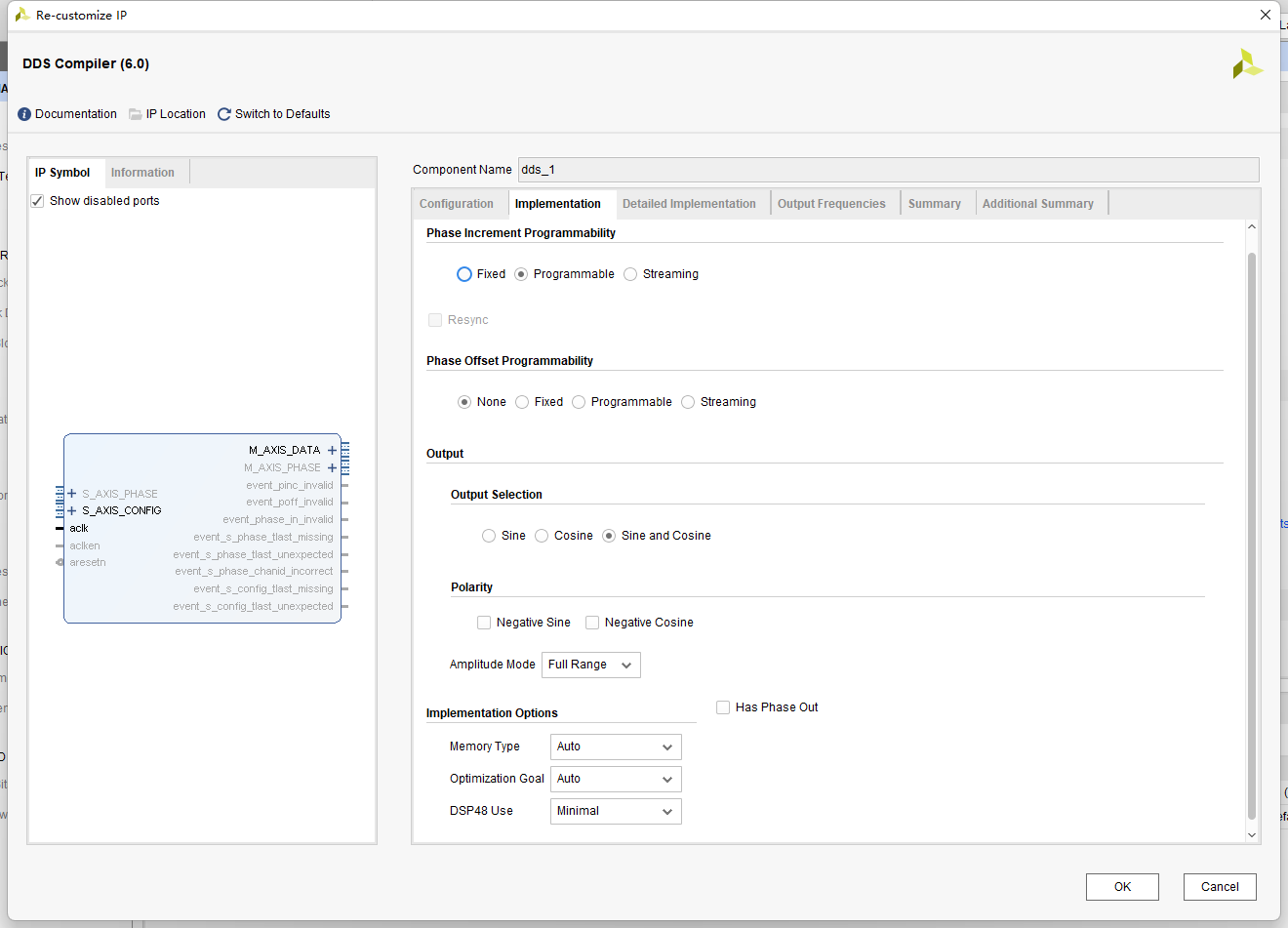

1处:相位增量是否支持可编程配置

Fixed是固定相位增量,DDS运行过程中不可更改,即对应不可变频率;

Programmable可编程,选中后出现配置接口,可在DDS运行过程中随时写入频率控制字改变输出波形的频率,用于偶尔改变频率;

Streaming应用于频繁改变频率,或者FM频率调制;

2处:相位偏移是否支持可编程配置

None不支持;

Fixed固定相位偏移;

Programmable可编程配置(偶尔改变);

Streaming经常改变,应用于相位调制;

3处:输出波形选择

Sine只输出sin波形;Cosine输出cos波形;两个的位宽均为第一页设置的数据位宽,Sine and Cosine同时输出sin和cos波形,其中高位表示sin,低位表示cos,总的数据位宽加倍;

4处:极性选择

sin和cos波形默认使用的是有符号数,勾选相应的选项后,正负取反;

5处:幅度模式

Full Range:全精度(全范围),针对通信应用,需要最大振幅,但由于自动增益控制导致振幅的值不那么重要的场合,输出幅度接近1;

Unit Cycle:单位圆,用于对DDS输出振幅值要求很高的应用,比如产生FFT旋转因子。单位圆时,DDS输出幅值为半全量程(即取值范围为01000..(+ 0.5)。110000 . .(-0.5))。

6处:是否输出相位信息

勾选后含有相位输出通道,不勾选时只输出幅度信息M_AXIS_DATA;

7处:使用的存储资源类型

Auto由具体所需的资源决定,资源较少时使用DROM,资源多时选择BROM;DistributeROM选择分布式ROM(DROM),Block ROM选择块ROM资源(BROM);

8处:综合优化策略

Area是面积优先,尽可能节省资源用量(LUT、FF等),Speed速度优先,尽可能提升性能;

9处:DSP48资源的使用策略

Minimal尽可能少用,节省资源,Maximal尽可能多用,提高性能;

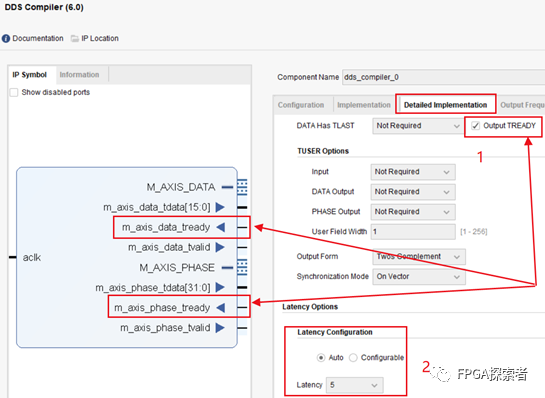

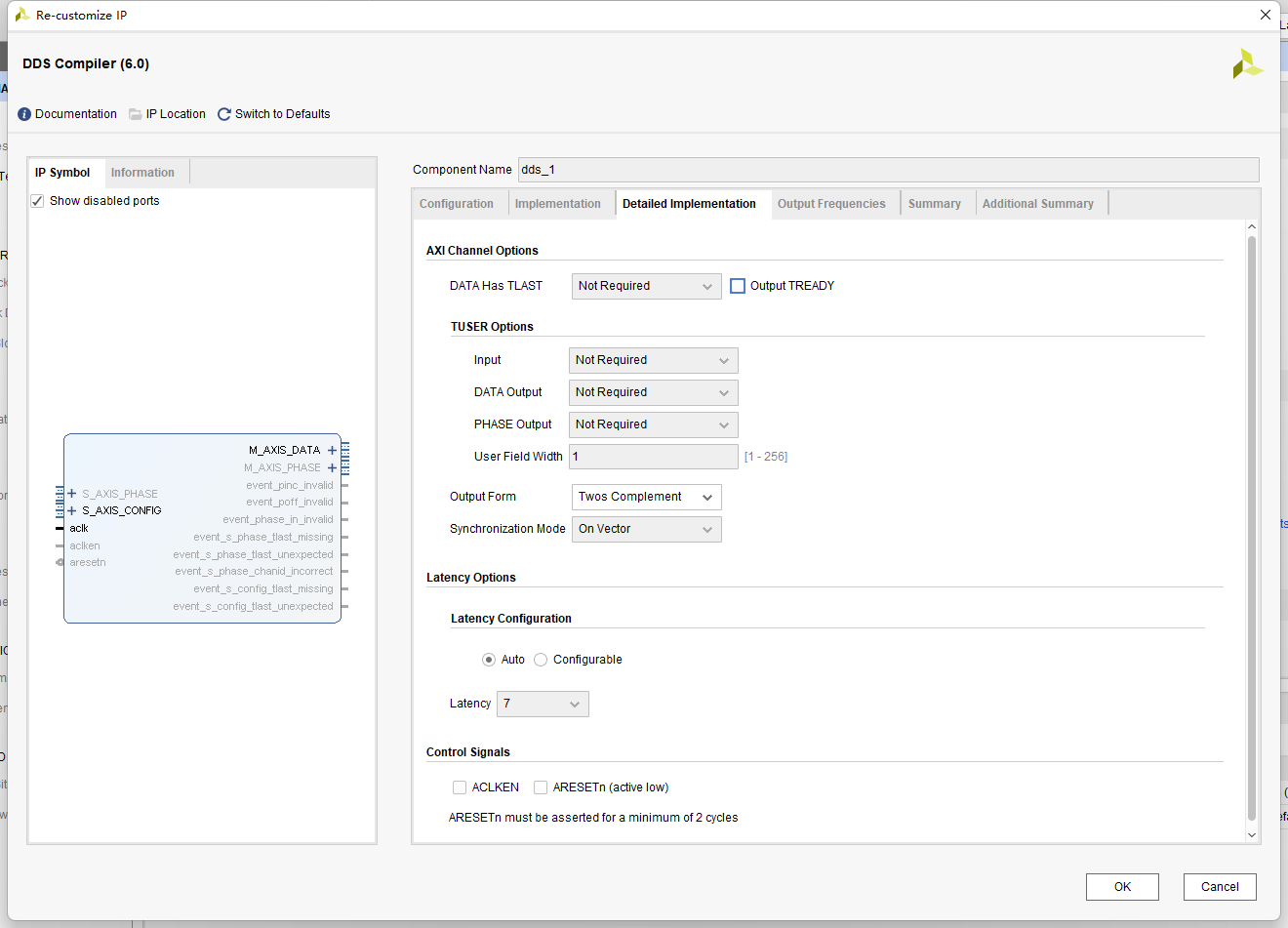

单通道模式下,总线的配置只包含可选的输出信号的Ready。多通道模式下,通道可选是否包含tlast等信号。

1处:输出ready信号

选中则输出的2个通道中增加tready信号(可选),根据AXI_Stream总线协议的规则,由后级接收模块输入一个ready信号(高电平),表示已经准备好接收DDS输出,此时DDS才能输出;

2处:延时配置

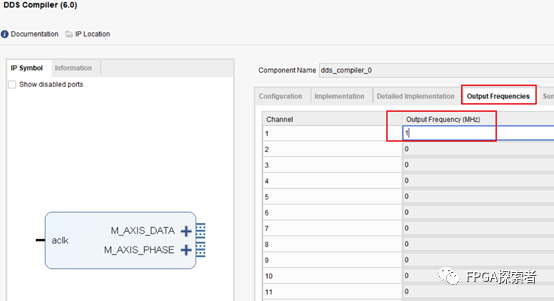

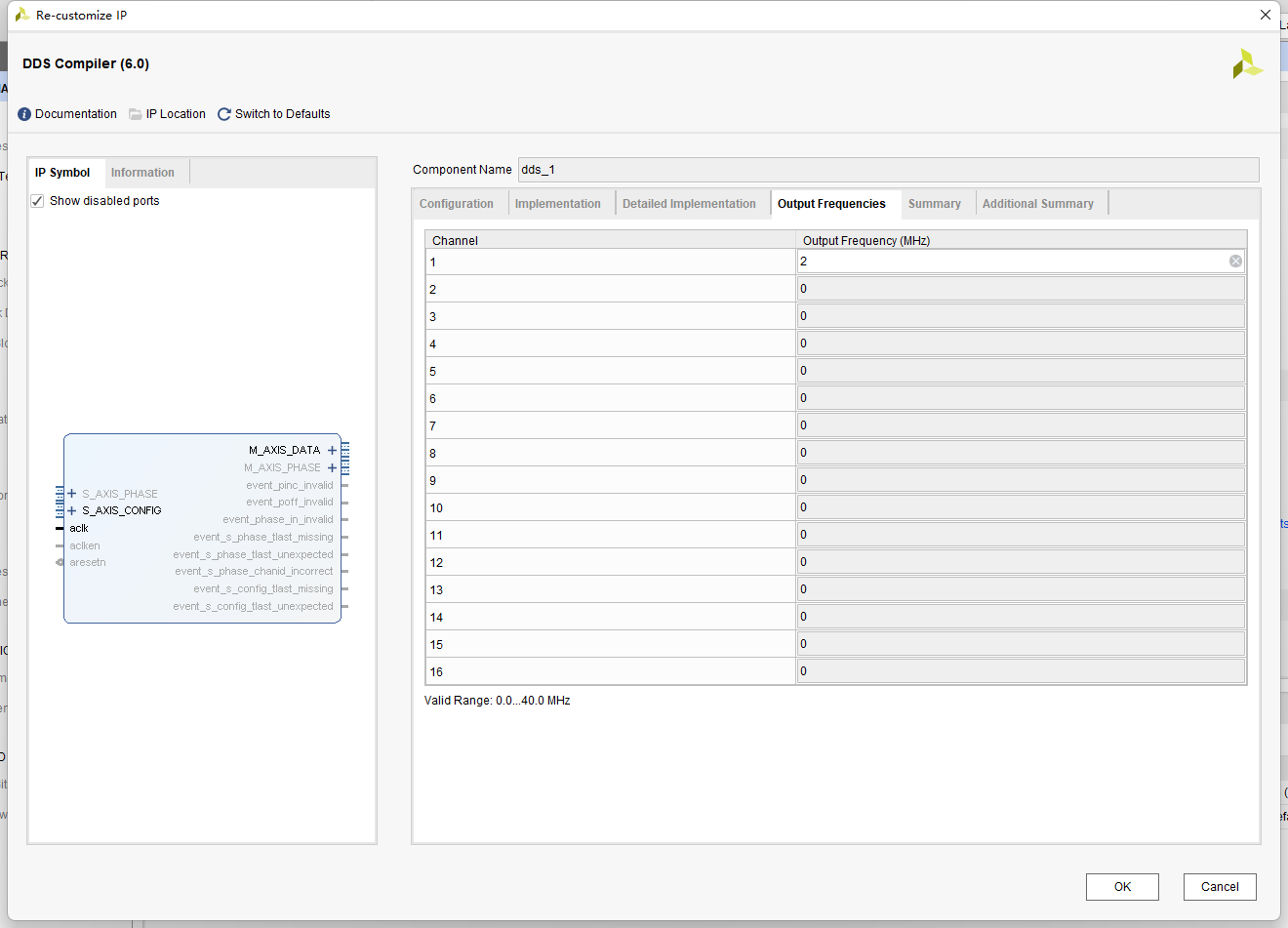

配置各通道的输出频率,在第一页中只使用了1个Channel,所以此处只能配置一个通道,直接配置输出频率,单位MHz,比如0.02MHz;

进行设计:

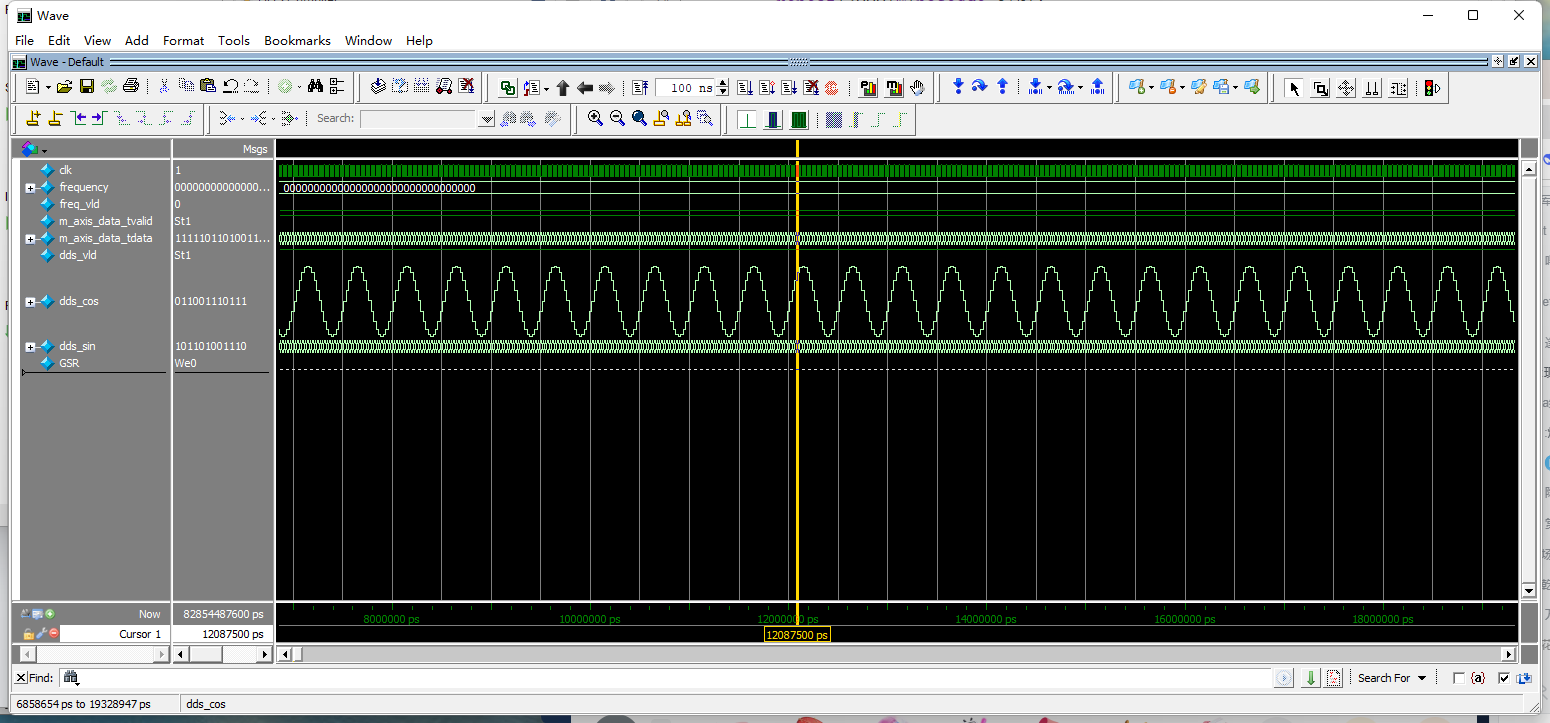

`timescale 1ns / 1ps

module sys_sim();

reg clk;

reg [31:0] frequency;

reg freq_vld;

wire m_axis_data_tvalid;

wire [31:0] m_axis_data_tdata;

wire dds_vld;

wire [11:0] dds_cos;

wire [11:0] dds_sin;

assign dds_vld = m_axis_data_tvalid;

assign dds_cos = m_axis_data_tdata[11:0];

assign dds_sin = m_axis_data_tdata[27:16];

// parameter SYS_CLK = 40000000; //system clock 40M

// parameter CLK_6M = 6000000; //frequency 6M

// parameter CLK_400K = 400000; //frequency 400K

// parameter CLK_2M = 2000000; // frquency 2M

// parameter PHASE_WIDTH = 32 ; // 相位宽度为32bit

// clock

initial begin

clk = 0;

forever #(12.5) clk = ~clk; // 40M system clokc

end

initial begin

frequency = 'd0;

freq_vld = 1'b0;

repeat(3000)@(posedge clk);

// 产生一个频率为400KHz的复指数

frequency = 32'd42949672; //CLK_400K * (2^PHASE_WIDTH)/SYS_CLK

freq_vld = 1'b1;

@(posedge clk)

freq_vld = 1'b0;

repeat(3000)@(posedge clk);

// 产生一个频率为4MHz的复指数

frequency = 32'd214748364 ;//CLK_4M * (2^PHASE_WIDTH)/SYS_CLK

freq_vld = 1'b1;

@(posedge clk)

freq_vld = 1'b0;

repeat(3000)@(posedge clk);

// 产生一个频率为6M的复指数

frequency = 32'd644245094;// CLK_6M* (2^PHASE_WIDTH)/SYS_CLK

freq_vld = 1'b1;

@(posedge clk)

freq_vld = 1'b0;

end

dds_1 inst_dds (

.aclk(clk), // input wire aclk

.s_axis_config_tvalid(freq_vld), // input wire s_axis_config_tvalid

.s_axis_config_tdata( frequency), // input wire [31 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata) // output wire [31 : 0] m_axis_data_tdata

);

endmodule

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)