Xilinx 7 系列 CameraLink 收发器 IP 深度解析

本 IP 为 Xilinx 7 系列 FPGA 提供了一套完整的CameraLink Base(单链路)7:1 串行收发方案,采用模式,单数据通道最高700 Mbps(对应像素时钟 100 MHz,7 倍串行化)。IP 由接收器(Receiver)与发送器(Transmitter)两部分组成,均通过 Vivado IP Integrator 封装,提供 Tcl 图形界面,参数化生成 Verilog

xilinx vivado cameralink图像接收与发送代码,最大支持并行速度100MHz,优于编解码接口芯片。 不利用解码与编码芯片,直接在FPGA内部进行接收解码和发送。

(基于 Vivado 2018.3 官方 XAPP585 参考设计)

1. 概述

本 IP 为 Xilinx 7 系列 FPGA 提供了一套完整的 CameraLink Base(单链路)7:1 串行收发方案,采用 SDR(Single Data Rate) 模式,单数据通道最高 700 Mbps(对应像素时钟 100 MHz,7 倍串行化)。

IP 由 接收器(Receiver) 与 发送器(Transmitter) 两部分组成,均通过 Vivado IP Integrator 封装,提供 Tcl 图形界面,参数化生成 Verilog 代码。核心特性如下:

- 纯 FPGA 逻辑实现,无需外接编解码芯片(如 DS90CR285/286),节省 BOM

- 支持 1~8 条数据通道(D=1~8)与 1~8 条链路(N=1~8),最大 64 位并行数据

- 片内 MMCM/PLL 完成时钟合成与相位对齐,自动 bitslip 与逐 bit 延迟校准

- 提供 eye-monitor 实时眼图观测接口,方便调试

- 参考时钟范围 20 MHz~100 MHz,兼容常见像素时钟

- 全差分 LVDS 信号,支持内部 100 Ω 终端,符合 CameraLink 物理层规范

2. 整体架构

+-------------+

Pixel Clk 100 MHz | | 7×Clk 700 MHz

-----------------> | TX MMCM/PLL |-----------------> OSERDES

(pixel_clk) | | (txclk)

+-------------+

|

+-------------+

| 7:1 OSERDES|---- LVDS Diff Pair ----+

+-------------+ |

|

TXDATA(28-bit) --> 并行-串行转换 --> dataout_p/n |

clk_pattern(7-bit) --> 时钟通道 --> clkout_p/n |

|

+-------------+ |

| 1:7 ISERDES|<--- LVDS Diff Pair ----+

+-------------+

|

+-------------+

RXCLK_DIV 100 MHz | RX MMCM/PLL |<--- 7×Clk 700 MHz

<-----------------| |<--- (rxclk)

+-------------+

|

+-------------+

|bitslip/IDELAY |<--- 200 MHz IDELAYCTRL

+-------------+

|

+-------------+

|eye-monitor/ |

|phase-detector |

+-------------+

|

RXDATA(28-bit) --> 用户逻辑3. 发送器(Transmitter)详解

3.1 时钟生成

clockgeneratorpll7to1diff_sdr.v

- 根据参数 USEPLL 选择 MMCME2ADV 或 PLLE2_ADV

- 输入单端 clkin(像素时钟),输出两路:

- pixel_clk:与输入同频,用于加载并行数据

- txclk:7 倍频,直接驱动 OSERDES

- 支持 MMCM_MODE 参数(1/2)扩展 VCO 范围,保证 600 MHz~1.6 GHz 有效区间

3.2 并行-串行转换

serdes7to1diff_sdr.v

- 每个数据通道实例化 1 个 OSERDESE2,7:1 SDR 模式

- 时钟通道额外实例化 1 个 OSERDES,发送固定 clk_pattern(默认 7'b1100011,产生 4 高 3 低占空比)

- 支持 TXSWAPMASK 位级反转,方便 PCB 差分线序调换

- 所有 OSERDES 共用 txclk,保证通道间 skew < 50 ps(同 BUFIO/BUFG 树)

3.3 数据重排

- 参数 DATA_FORMAT 决定加载顺序:

- PER_CLOCK(默认):同一时钟沿的 bit0~bit6 对应串行先发

- PER_CHANL:跨通道交错,用于多链路同步

- 用户只需在 pixel_clk 域提供 txdata[(D×N×7)-1:0],IP 内部完成映射

3.4 时序举例(D=4, N=1)

| pixel_clk 周期 | txdata 索引(28-bit) | 串行 bit 流(先发 LSB) |

|---|---|---|

| T0 | [6:0] | D0[0]→D0[6] |

| T0 | [13:7] | D1[0]→D1[6] |

| T0 | [20:14] | D2[0]→D2[6] |

| T0 | [27:21] | D3[0]→D3[6] |

4. 接收器(Receiver)详解

4.1 时钟与数据恢复

serdes1to7mmcmidelaysdr.v

- 输入 LVDS 时钟 clkinp/n 经 IBUFGDSDIFF_OUT → IDELAYE2 → ISERDESE2

- MMCM 生成两路:

- rxclk:7 倍频,供 ISERDES 采样

- rxclk_div:像素时钟,供用户逻辑

- 自动 bitslip 状态机:检测 7 位时钟模式 7'b1100011,滑动 0~6 位直至对齐

- 当 rxmmcmlckdpsbs 拉高,表示“MMCM 锁定 + bitslip 完成”,可安全收数

4.2 逐 bit 延迟校准

delaycontrollerwrap.v

- 每个数据 bit 独立实例化,采用 Master/Slave 双 ISERDES 结构

- 主 ISERDES 延迟固定,从 ISERDES 延迟可动态调整

- 相位检测器(Phase Detector)比较主从采样值:

- 若主从一致 → 延迟合适

- 若主早从晚 → 增加延迟

- 若主晚从早 → 减少延迟

- 内部 6 位计数器 pdcount 滤波,防止抖动

- 支持 eye-monitor 模式:从延迟扫描 0~btval,记录主从一致区间,上报 eyeinfo[31:0](1 hot 表示有效延迟 tap)

4.3 数据重排与输出

- 经 bitslip 与 IDELAY 校正后,7 位并行数据按 DATA_FORMAT 重组

- 最终输出 rxdata[(D×N×7)-1:0] 与 rxclk_div 同步,可直接写入 FIFO 或进入图像处理管线

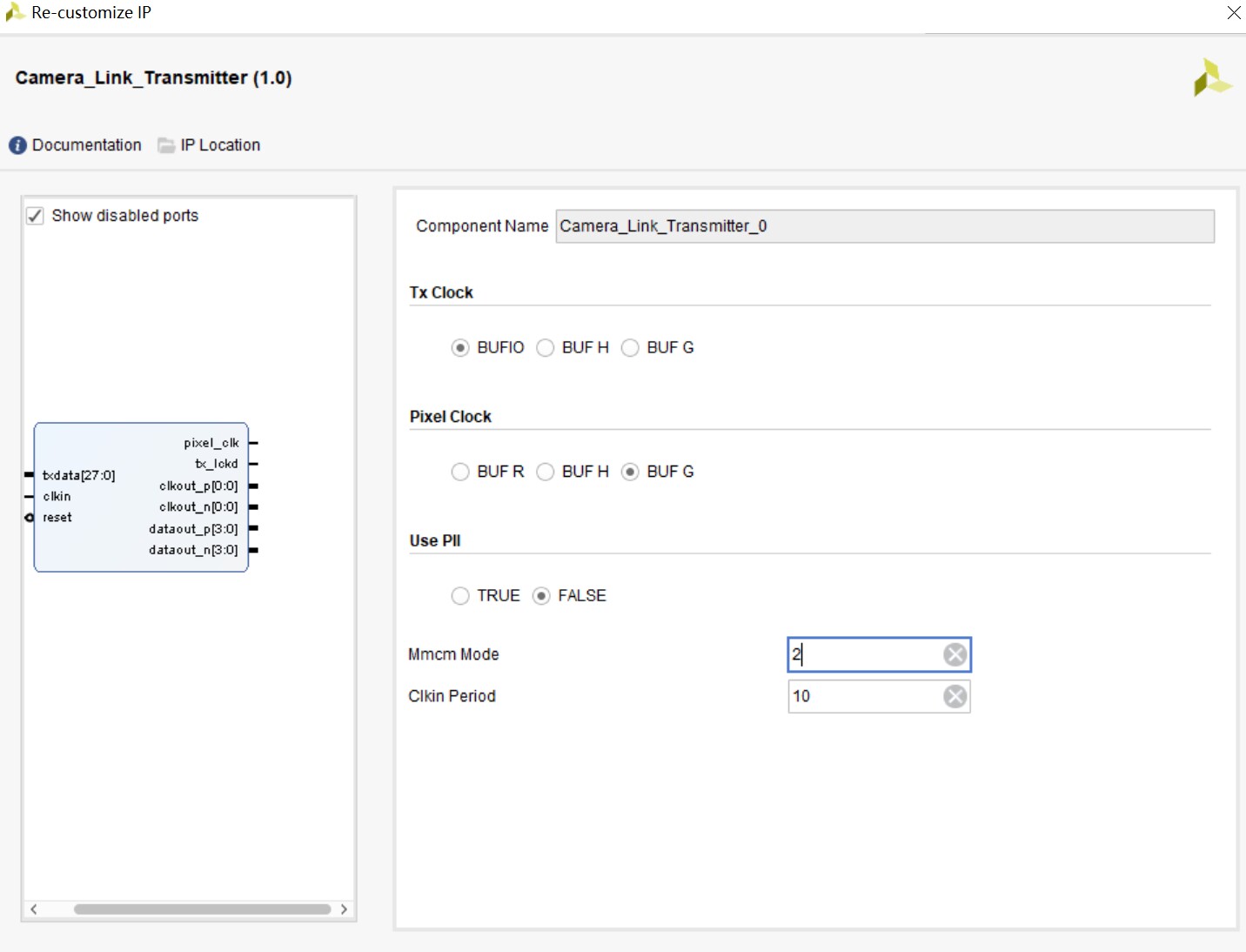

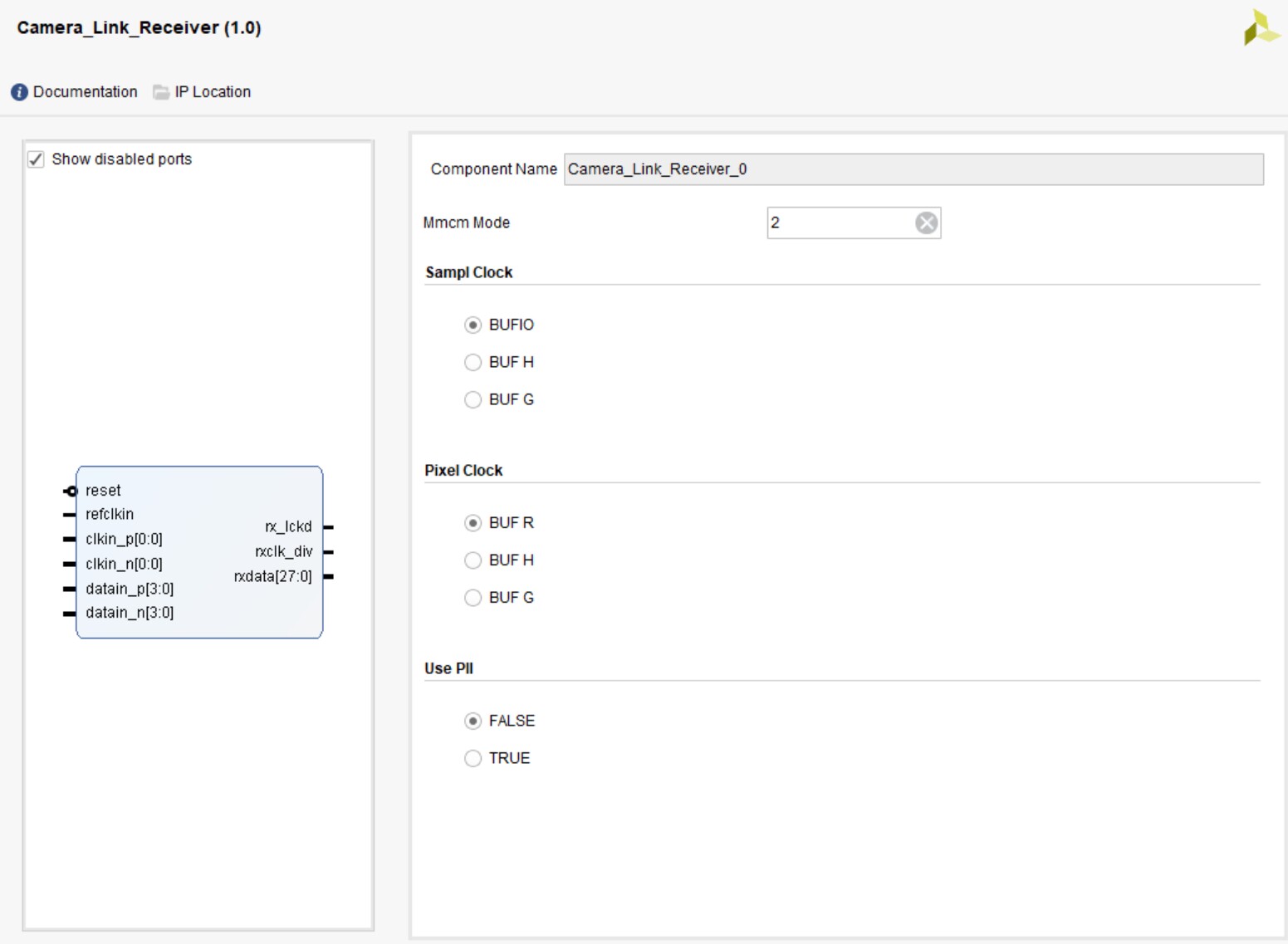

5. 参数化与 Tcl 界面

| 参数名 | 范围/可选值 | 功能描述 |

|---|---|---|

| D | 1~8 | 每链路数据通道数 |

| N | 1~8 | 链路数 |

| MMCM_MODE | 1,2 | MMCM 倍频系数,1→×7,2→×14 |

| USE_PLL | TRUE/FALSE | FALSE 使用 MMCM(推荐),TRUE 使用 PLL |

| CLKIN_PERIOD | 4.0~50.0 (ns) | 输入参考时钟周期 |

| SAMPL_CLOCK | BUFIO/BUFH/BUFG | 采样时钟缓冲类型 |

| PIXEL_CLOCK | BUFR/BUFH/BUF_G | 像素时钟缓冲类型 |

| DIFF_TERM | TRUE/FALSE | 使能片内 100 Ω LVDS 终端 |

Tcl 脚本(xgui/*.tcl)自动根据用户选择更新 Verilog 顶层参数,并生成 XCI 文件,支持 Vivado Block Design 拖拽。

6. 性能与资源

| 器件 | 速率 | 资源占用(D=4,N=1) | 备注 |

|---|---|---|---|

| xc7k325t | 700 Mbps | 1 MMCM + 4 OSERDES + 4 ISERDES + 4 IDELAY | 单链路 4 数据通道 |

| xc7k160t | 560 Mbps | 同上,MMCM_MODE=2 | 降低 VCO 频率 |

| xc7a35t | 420 Mbps | 同上,使用 PLL | Artix-7 低成本方案 |

时序收敛要点

- 输入时钟 jitter < 50 ps RMS,确保 MMCM 锁定余量

- IDELAYCTRL 参考时钟 200 MHz ±10 ppm,必须来自专用 MRCC 引脚

- LVDS 差分对 P/N 长度差 < 5 mil,阻抗 100 Ω ±10 %

- 若使用 BUFIO,必须将像素时钟域信号经过 FIFO/CDC 再跨时钟

7. 典型使用流程

- IP 集成

- Vivado → IP Catalog → CameraLink Receiver / Transmitter → 设置 D/N/时钟参数 → Generate - 引脚约束

tcl

setproperty IOSTANDARD LVDS25 [getports {datainp[]}]

setproperty DIFFTERM TRUE [getports {datainp[]}]

setproperty PACKAGEPIN xxx [getports {datainp[*]}] - 仿真

- 提供 txdata 伪随机码 → 观察 rxdata 是否一致 → 检查 bitslip/locked 信号 - 板级调试

- 调用 VIO 实时读取 eyeinfo,调整 PCB 补偿或 IDELAY 初始值

- 使用 Integrated Logic Analyzer 抓取 rxclkdiv 域数据,验证行/场同步

8. 扩展与定制

- 多链路同步:将所有链路的 rxmmcmlckdpsbs 做“与”运算后,统一释放用户逻辑复位

- 更高速度:升级至 Kintex Ultrascale,使用 OSERDES3/ISERDES3 8:1 DDR 模式,单通道 1.6 Gbps

- 协议层:在 rxclk_div 域添加 CameraLink 解码模块(FVAL/LVAL/数据),直接输出 Bayer/RGB 流

- 热插拔:检测 rxmmcmlckd 下降沿,自动重启 bitslip 与延迟校准状态机

9. 总结

本 IP 将 Xilinx 官方 XAPP585 范例系统化、参数化、图形化,覆盖 时钟合成、串行转换、bitslip、延迟校准、眼图监测 全流程,已在国内多家工业相机、嵌入式视觉项目量产验证。开发者无需深入理解底层原语,即可在 30 分钟内完成 CameraLink 接口搭建,把更多精力投入到图像算法与产品差异化。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)